## Introducing STM32 L0x Series

April 2014

### www.emcu.it

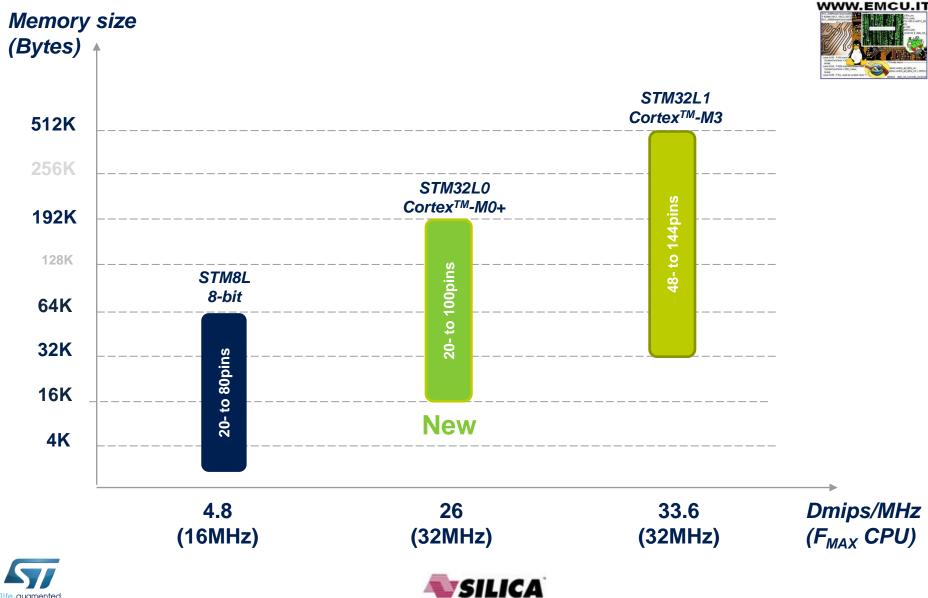

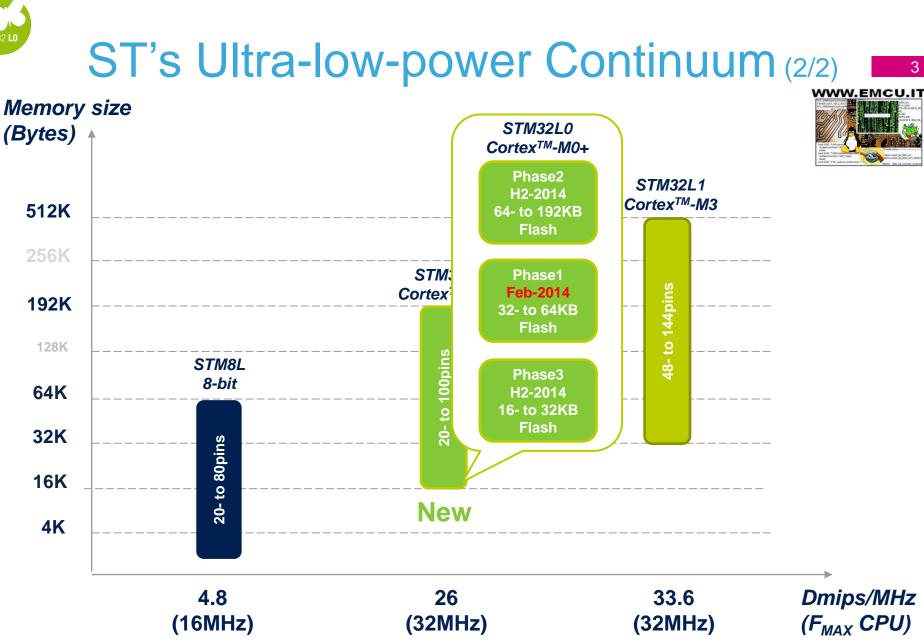

# ST's Ultra-low-power Continuum (1/2)

2

## Meet with STM32L0x Series

### STM32<sup>®</sup> ultra-low-power DNA is now built with ARM Cortex-M0+

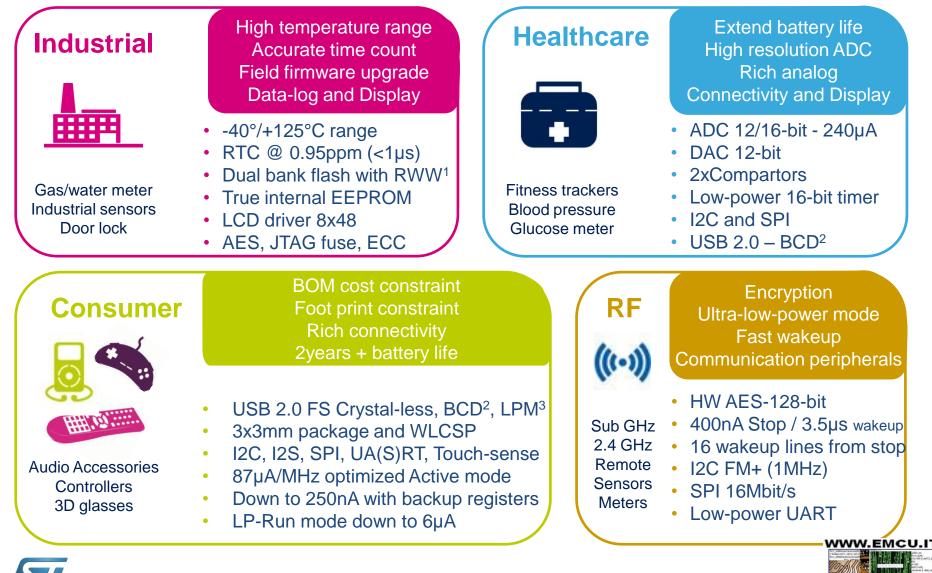

### **Targeted** applications

Read While Write operation (Execute code from Flash while writing in the EEPROM **Battery Charger Detection** 2.

- Link Power Management 3.

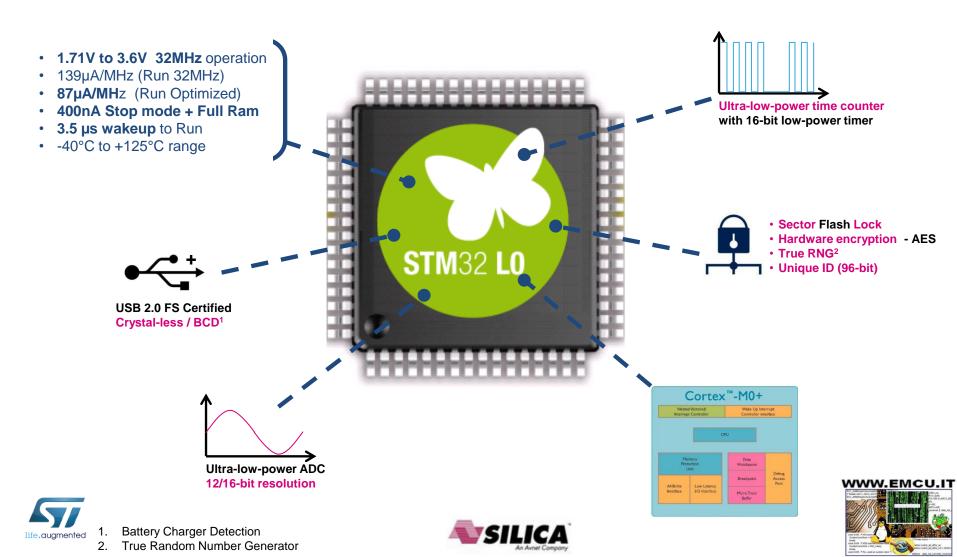

STM32L0 is simply ...

#### BETTER

- 139 μA/MHz (at 32MHz) down to 87 μA/MHz (optimized mode) in Run

- 440nA in Stop mode with Full RAM retention and Low-power Timer Counter (LTC)

- 3.5 µs wakeup time

- 1.71V to 3.6V 32MHz range

#### SMARTER

- Independent clock domain for communication peripheral

- ADC 12/16-bit resolution with only 48µA in 12-bit 100ksps mode (200µA at 1,14Msps)

- USB 2.0 Crystal-less, BCD, LPM

- Build-in LCD driver

- True EEPROM embedded

- Pulse counter and low-power UART

#### SMALLER

- 3x3mm 20pins package down the road

- CSP package below 5mm<sup>2</sup>

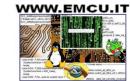

### STM32 L0x – Product lines

DAC

2x 12-bit

DAC

2x 12-bit

SILICA

USB2.0

Crystal

Less,

LPM, BCD

**USB2.0**

Crystal

Less,

LPM, BCD

Touch

Sense

Touch

Sense

True

RNG

True

RNG

|  | 1 | 7 |

|--|---|---|

|  |   |   |

LCD

8x48

4x52

| Common features                                           | STM32                                 | L0x3 – L      | JSB & L(                | CD line -                      | - 32-K to                  | 192-K       | oyte Flas                       | sh      |

|-----------------------------------------------------------|---------------------------------------|---------------|-------------------------|--------------------------------|----------------------------|-------------|---------------------------------|---------|

| Cortex <sup>™</sup> -M0+ 32 MHz speed<br>with MPU and MUL | Up to<br>192-KB<br>Flash <sup>1</sup> | 16-KB<br>SRAM | Up to<br>6-KB<br>EEPROM | Main osc.<br>input<br>1-24 MHz | RTC with<br>32 kHz<br>osc. | 7 ch<br>DMA | ADC<br>12-bit<br>1Msps          | ا<br>2x |

| AES 128-bit                                               |                                       |               |                         |                                |                            |             | 12-ch                           |         |

| Firewall protection <sup>2</sup><br>(Flash and RAM)       |                                       |               |                         |                                |                            |             |                                 |         |

| Built-in 16 MHz, 4,2MHz and 38<br>kHz RC oscillators      | STM32                                 | L0x2 – l      | JSB line                | - 32 to 7                      | 192-Kbyt                   | e Flasi     | า                               |         |

| Multiple USART, SPI, I2C<br>Low-power UART                | Up to<br>192-KB<br>Flash <sup>1</sup> | 16-KB<br>SRAM | Up to<br>6-KB<br>EEPROM | Main osc.<br>input<br>1-24 MHz | 32 kHz                     | 7 ch<br>DMA | 12-bit<br>ADC<br>1Msps<br>12-ch | 2x      |

| Multiple 16-bit timers<br>Low-power 16-bit timer          |                                       |               |                         |                                |                            |             |                                 |         |

| 2x watchdogs                                              |                                       |               |                         |                                |                            |             |                                 |         |

| Reset circuitry POR/PDR                                   | STM32                                 | L0x1 – A      | Access I                | ine - 16-I                     | K to 192-                  | Kbyte       | Flash                           |         |

| Brown Out Reset<br>Program Voltage Detector               | Up to<br>192-KB<br>Flash <sup>1</sup> | 16-KB<br>SRAM | Up to<br>6-KB<br>EEPROM | Main osc.<br>input<br>1-24 MHz | 32 kHz                     | 4 ch<br>DMA | 12-bit<br>ADC<br>1Msps          |         |

| 2x comparators                                            | Tasti                                 |               |                         | 1-24 10112                     | - 030.                     |             | 12-ch                           |         |

| Dynamic Voltage Scaling                                   |                                       |               |                         |                                |                            |             |                                 |         |

1. Dual bank flash with Rww feature from Flash to EEPROM (on part number > 128KB Flash)

2. Only on STM32L0x2 and L0x3 line

life.augmented

### STM32LOx – portfolio Cortex<sup>TM</sup>-M0+ @ 32MHz – 100+ P/N

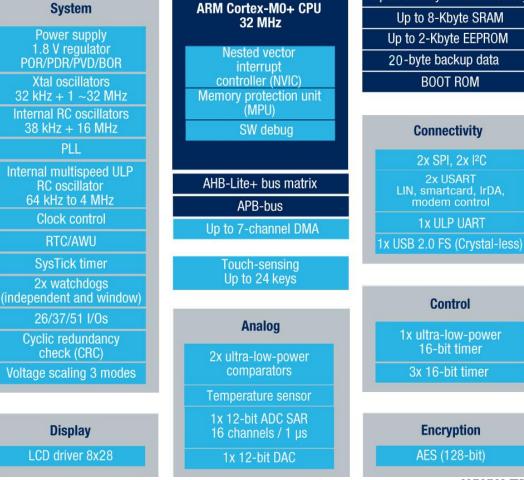

# STM32L05x block diagram

#### Key features

- ARM Cortex-M0+ at 32MHz

- Single-cycle I/O access

- Single-cycle multiplier (MUL)

- 0.97 DMIPS/MHz

- 1.71V to 3.6V, 32MHz full functional

- Digital down to 1.65V

- -40°C to +125°C temperature range

- ADC with build-in HW oversampling

- Flash + Ram code sector lock

- USB 2,0 FS certified

- Build-in 48MHz oscillator

- Battery Charger Detection

- Link Power Management

- Independent clock domain

- I2C, USART/UART

- USB

- 3x timers

- 1x 16-bit (4ch)

- 2x 16-bit(2ch)

- 1x 16-bit LP<sup>1</sup> available in stop

Up to 64-Kbyte Flash memory

| FICE APEPvright                        | ADC2, ADC3          |              | 词 D#18      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------|---------------------|--------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nad                                    | Sline               |              | a 191       | ALL PROVIDED AND A CONTRACT AND A CO |

|                                        |                     |              |             | Billey.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        | 1800                |              |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| sate 0.00 PA<br>SystemCareO            |                     | 1            |             | Eth ISA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| sase 0:04: 7 h<br>SystemCoreO<br>break | SE used all stream  | -            | witten pre- | RALARIAN RALARIAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1814 0100 73                           | \$1, used as system | stock of the | -           | als not correctly received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

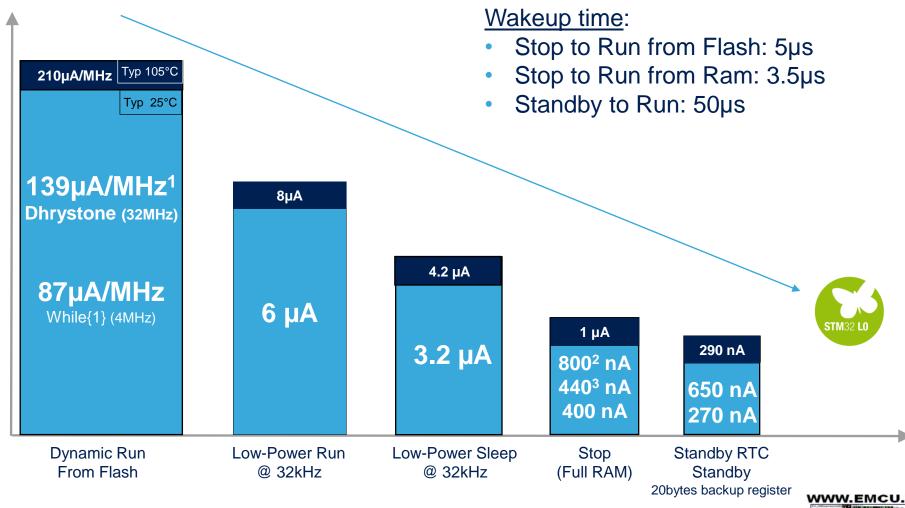

### STM32L05x - power consumption 10

#### Typ current

1. 2. 3.

. Dhrystone power consumption value executed from Flash with VDD=3.3V

. STOP mode consumption with : Full Ram retention + RTC (32,768kHz)

3. STOP mode consumption with : Full Ram retention + LTC (Low-power Time Counter)

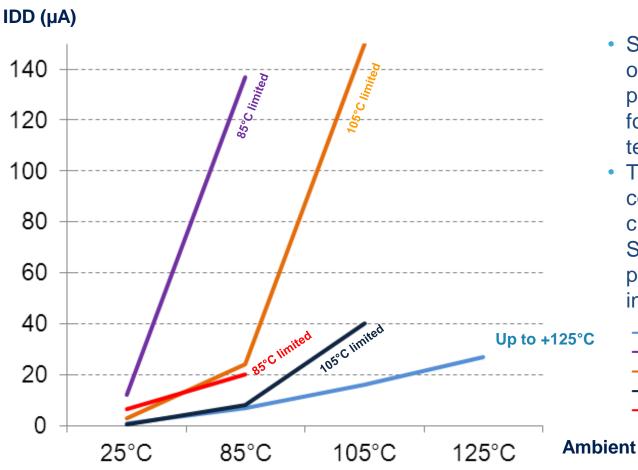

### Leader at high temperature 11

• Max. current value at lowest power mode vs. temperature capability

- STM32L0 platform offers the lowest power consumption for the highest temperature range.

- This capability to control leakage current makes STM32L0 the premium choice for industrial application,

STM32L0

Competitor A

Competitor F Competitor R Competitor T

Note: Value based on competition datasheet, looking at lowest power mode with full RAM retention at VDD 3.0V. All datasheet give same value for -40°C/+25°C temperature range.

- Why is STM32L0 SMARTER ?

- ADC: The lowest current consuming of the Industry

- 48 μA only at 100Ksps with 12-bit resolution (max speed: 1.14Msps 200 μA)

- 16-bit resolution capable thanks to built-in hardware oversampling feature

- DMA capability

- DAC:

- 12-bit DAC with output buffer

- External triggers and input reference voltage capable

- DMA capability (with underrun interrupt)

- Comparator

- 2x built-in comparator ext./int. ref. voltage capable

- Stop mode wake up capable

- Window comparator mode capable

- For which application ?

Gas/Water meter

Door lock

### Communication peripheral set

- Why is STM32L0 SMARTER ?

- USB 2.0 FS Crystal-less: with Integrated 48 MHz oscillator

- BCD (Battery Charging Detection) with 1.5A max and LPM (Link Power Management) capable

- USB device library and USB VIP/PID sublicensing service for free

- I2C: Independent clock domain + wakeup from stop

- Multi-master or Slave modes capable (7 and 10-bit addressing)

- Support Fast mode + (up 1 Mbits/s) and SMBus/PMBus

- USART: Independent clock domain + wakeup from stop

- Support ISO7816, IrDA SIR ENDEC, LIN Master/slave and auto baud rate feature

- Low-power UART: com. available in stop mode

- Snooze wakeup mode capable

- SPI: Full duplex, half duplex up to 16 Mbits/s

- Support basic SD Card/MMC modes

- Built-in I2S with audio sampling freq. fro 8 kHz to 192 kHz.

- For which application ?

#### Other peripheral set

### • Why is STM32L0 SMARTER ?

- Timers:

- Up to 8 timers with 5x 16-bit

- · Low-power 16-bit asynchronous timer available in stop mode

- 16bit up counter, 16-bit compare register, software or hardware trigger

- Output: pulse, PWM

- Encoder mode, and programmable glitch filter

- Pulse counter mode

- System safety and security

- Independent Watchdog (clocked from internal 37kHz osc.) and Window watchdog

- CSS (Clock Security System)

- Dynamic switch to MSI(Multi Speed Internal clock) in case of HSE clock failure

- Wakeup event or interrupt generated in case of LSE(Low Speed External clock) clock failure

Wireless solution < 1GHz or 2.4GHz

- Built-in HW encryption with AES 128-bit (AES 256-bit available with free crypto lib)

- CRC and Unique ID (96-bit)

- JTAG fuse option and Readout code sector protection

- Error Correction Code (ECC) available for both Flash and EEPROM

### • For which application ?

Industrial sensors

Display card

# STM32L0x – Ecosystem 15

#### Evaluate, Discover and Play

### Feel free to choose your IDE

GCC based toolchains

#### Software offer

#### STM32Cube<sup>™</sup>

- STM32CubeMX Software: Optimize you design layout, configure your microcontroller usage, and estimate your power consumption

- Embedded Software, from Hardware Abstraction Layer (HAL) easing migration from one STM32 to another, and middleware offer for STM32L0 like FreeRTOS and USB library