#### **Power 'n Motors**

Critical aspects in power applications design, proper component selection & experimental results

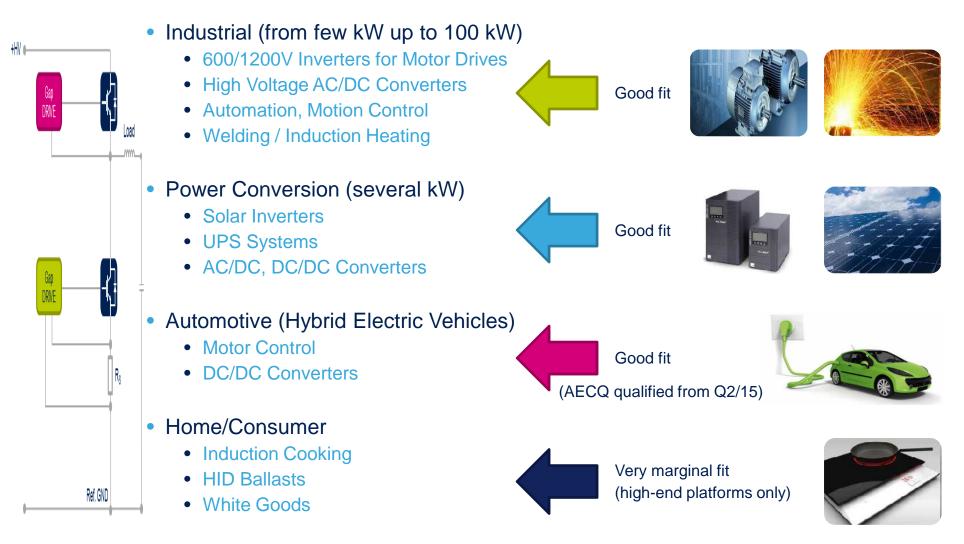

#### Target applications 2

Applications where an IGBT/MOSFET Driver with galvanic isolation can be implemented

#### Introducing STGAP1S

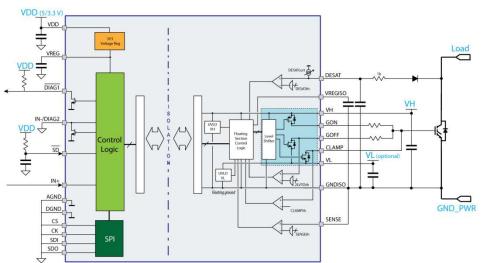

## gapDRIVE general overview

Galvanic isolated gate driver for IGBT and MOSFET in high demanding applications

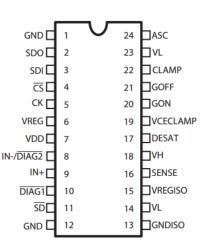

Package frame

STGAP1S (or "gapDRIVE")

On-chip isolation layer provides galvanic separation between input and control stage

To withstand the highest voltage up to 1500 V for enhanced robustness, noise immunity and design flexibility

Inductive coupling transfers the logic signal across the isolation with strong signal integrity and fast propagation

The SPI communication interface provides a complete and easy configurability as well as full digital diagnostics

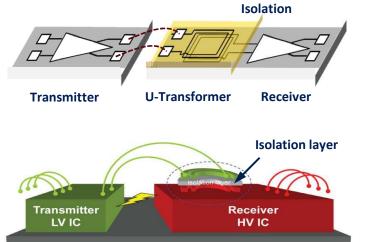

## What kind of insulation and why

- Power applications often require galvanic isolation due to:

- High side driving (functional isolation)

- Safety (galvanic isolation)

- Noise minimization (interference between LV/Logic part with HV/Power stage)

#### Integrated insulation guarantees cost and space savings

- Optical isolation

- Ageing of LED and transparent insulator lead to variation of propagation delay and reliability issues

- Limited dV/dt capability

- Capacitive coupling

- Prone to electrical field disturbance, therefore not well suited for high power applications

- Limited dV/dt capability as for the optical isolation

- Inductive coupling

- High immunity to magnetic field thanks to coil topology

- Very good dV/dt capability (>50 V/ns)

- Transfer of logic signals across a <u>4 kV</u> galvanic isolation (maximum surge insulation voltage)

### Insulation Characteristic 6

#### IEC60664-1, IEC60747-5-2 and UL1577 standards

| Parameter                                                | Symbol            | Test Conditions                                                                                               | Characteristic    | Unit              |

|----------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|-------------------|-------------------|

| Maximum Working Insulation Voltage                       | V <sub>IORM</sub> |                                                                                                               | 1500              | $V_{PEAK}$        |

| Input to Output toot voltage                             | V <sub>PR</sub>   | Method a, Type and sample test $V_{PR} = V_{IORM} \times 1.6$ , $t_m = 10 \text{ s}$ Partial discharge < 5 pC | 2400              | V <sub>PEAK</sub> |

| Input to Output test voltage                             |                   | Method b, 100% Production test<br>$V_{PR} = V_{IORM} \times 1.875$ , $t_m = 1 s$<br>Partial discharge < 5 pC  | 2815              | V <sub>PEAK</sub> |

| Transient Overvoltage<br>(Highest Allowable Overvoltage) | V <sub>IOTM</sub> | t <sub>ini</sub> = 60 s                                                                                       | 4000              | V <sub>PEAK</sub> |

| Maximum Surge Insulation Voltage                         | V <sub>IOSM</sub> | t <sub>ini</sub> = 60 s                                                                                       | 4000              | $V_{PEAK}$        |

| Insulation Resistance                                    | R <sub>IO</sub>   | $V_{IO} = 500 \text{ V at } T_S$                                                                              | > 10 <sup>9</sup> | Ω                 |

| Parameter                                        | Symbol | Value | Unit | Conditions                                                                           |

|--------------------------------------------------|--------|-------|------|--------------------------------------------------------------------------------------|

| Creepage (Minimum External<br>Tracking)          | CPG    | 8     | mm   | Measured from input terminals to output terminals, shortest distance path along body |

| Comparative Tracking Index (Tracking Resistance) | СТІ    | ≥ 400 |      | DIN IEC 112/VDE 0303 Part 1                                                          |

| Isolation group                                  |        | II    |      | Material Group (DIN VDE 0110, 1/89, Table 1)                                         |

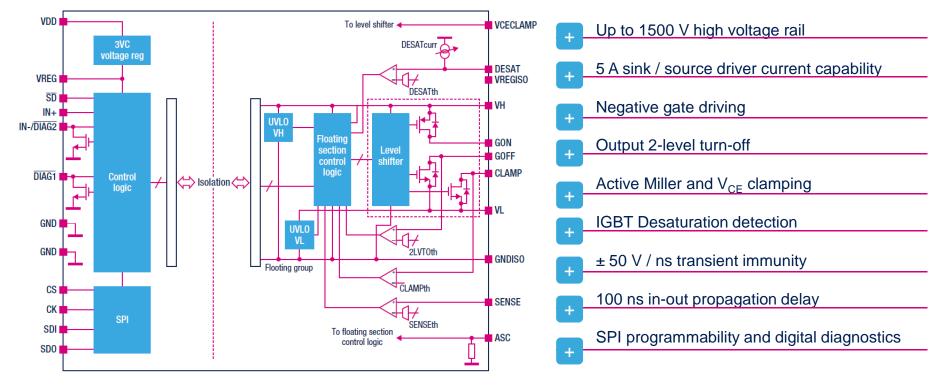

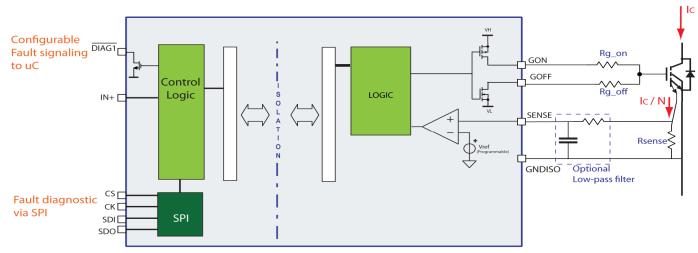

#### STGAP1S block and features overview 7

LV / Logic side

HV / Driving side

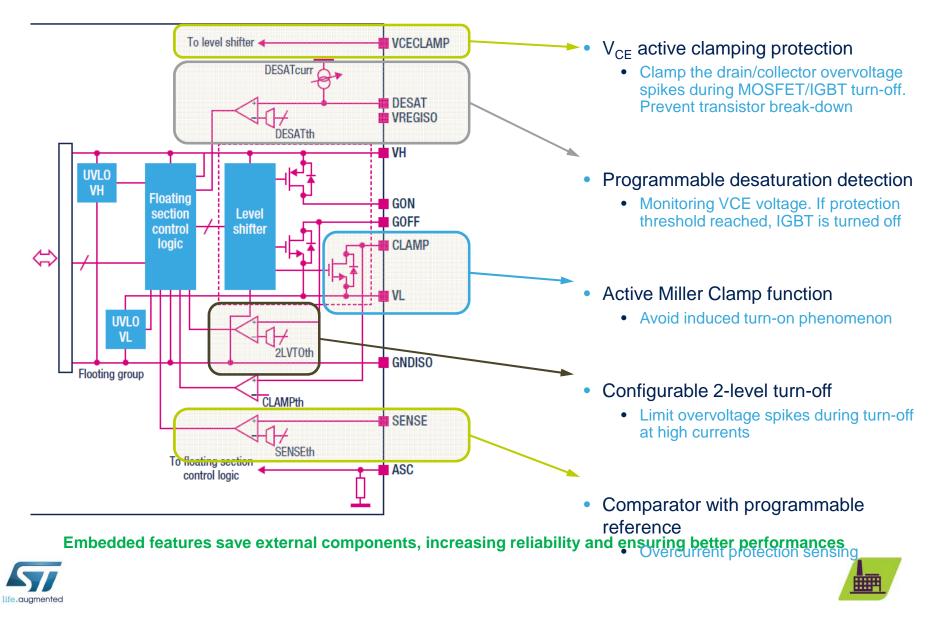

#### Output stage features highlights

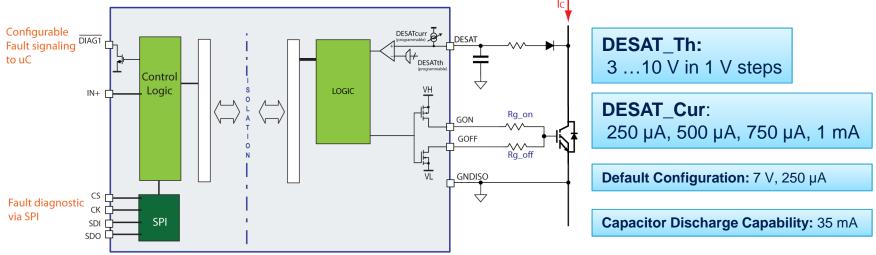

#### Desaturation detection for OCP

- In case the external IGBT desaturates, it may fail due excessive power dissipation: DESATuration protection monitors the VCE voltage and turns the IGBT off if a threshold voltage is reached

- At IGBT turn-on the protection's intervention is delayed for a fixed time called *blanking time* so to allow the IGBT to reach the saturation condition

- Both desaturation threshold and blanking current programmable via SPI

- Blanking current up to 1 mA allows better noise filtering without increasing blanking time

- Fault is transmitted to the fault registers in the low-voltage section. Event signaling to uC via DIAG pins is optional

## 2 Level Turn-Off in gapDRIVE

- 2LTO protects power switches from VCE overvoltage spikes during turn-off in case of overcurrent conditions

- 2LTO can be programmed to occur:

- At each cycle (like in TD350)

- Only after a DESAT or Over Current Event

- No need of the turn-on delay to avoid duty-cycle distortion

- No gate voltage reduction during t2LTO in normal conditions

- No minimum on-time required

- Never (disabled)

- Both 2LTO voltage and duration are programmable via SPI

- V<sub>2</sub>LTO: 16 values between 7 V and 14.5 V

- t<sub>2</sub>LTO: 16 values between 750 ns and 5.5 us

- 2LTO offers advantages vs. *Soft Turn-off* since it only slows down the turn-off speed for the minimum necessary time to avoid over-voltages, thus limiting the duration of the high-voltage high-current overstressing condition

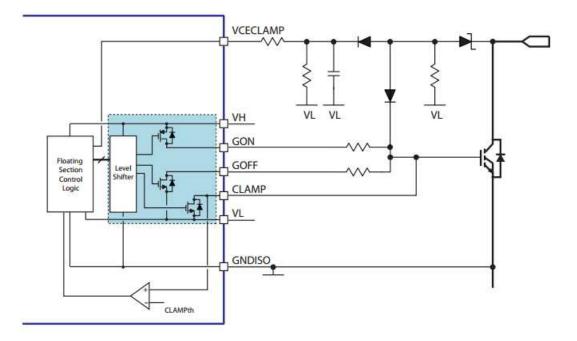

### V<sub>CE</sub> active clamping protection 11

- Ensuring protection against inductive V<sub>CE</sub> spikes during turn-off:

- Actively clamp the drain/collector overvoltage spikes during MOSFET/IGBT turn-off

- VCECLAMP is activated for a certain time (t<sub>VCECLoff</sub>) during the turn-off phase

- During this time the VCECLAMP can act on the driver's output status

- After the time expires, the driver works normally, ignoring the VCECLAMP pin status

Result: use of low turn-off resistor values leading lower turn-off losses, increasing efficiency and limiting maximum turn-off spike on drain/collector

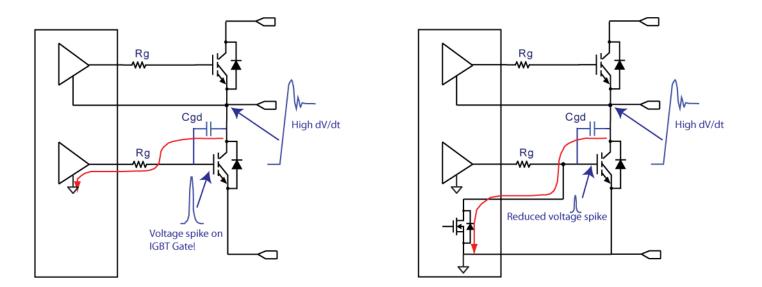

#### Active Miller CLAMP 12

- During fast collector rising transients current is injected towards the gate by the Miller capacitance (Cgd).

- A voltage spike appears on the switch gate, due to the drop caused by the Miller current across the overall gate path impedance (drivers RDs\_on + Rg)

- If such spike exceeds the switch Vth, a shoot through may occur across the half-bridge

- Active Miller Clamp avoids induced turn-on phenomenon

- Dedicated CLAMP pin has **5 A sink current capability**

## Current sensing for OCP

- In some applications Over-Current Protection is better achieved with current sensing through a shunt resistors rather than with DESAT

- Typical examples include low-current applications or applications using Current-sensing IGBTs

- The value of the internal threshold is probrammable via SPI

- 8 different values ranging from 100 mV to 400 mV can be selected

- Possibility to implement OCP also on High-Side switches

- More reliable short-circuit detection

- When an Overcurrent is detected the gate is immediately turned off, and the fault is transmitted to the fault registers in the low-voltage die. Direct event signaling to uC via

DIAG pins is possible

## Operation in default configuration 14

- DIAG1 pin provides information about:

- DESAT events

- VDD supply failure

- Missing VH

- Thermal shutdown

- SPI or register error (if SPI is used)

- IN-/DIAG2 configured as input

- Setting SD low for 10 µs clears errors

- All other features are disabled

Miller CLAMP DESAT VDESATth = 7 V, IDESAT = 250 µA VDD UVLO/OVLO VDD UVLO/OVLO Thermal Shutdown

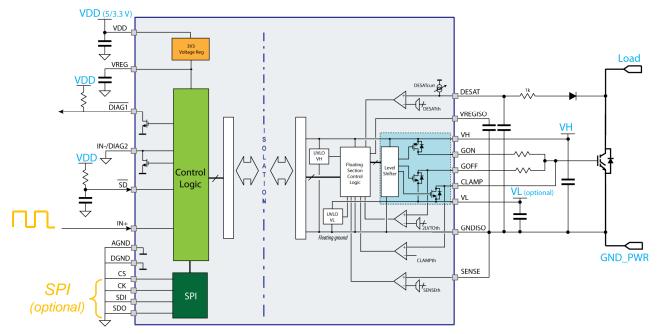

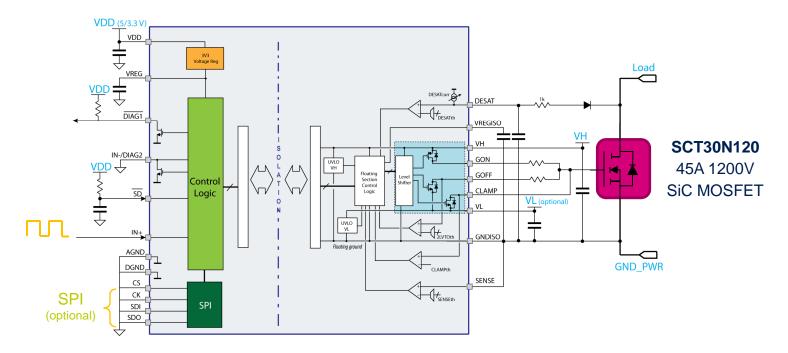

### STGAP1S driving SiC MOSFET 15

- Key requirements for driving SiC MOSFET:

- Positive gate drive +20V

- Negative gate drive -5V

- High current capability

- Key features supported by gapDRIVE:

- Positive gate drive up to +36V (VH + VL)

- Negative gate drive down to GNDISO-10V

- Up to 5A sink/source (@ 25°C)

- The newly introduced **SCT20N120** SiC MOSFET can be also driven by gapDRIVE

### STGAP1S basic configuration 16

- If VDD=3.3V required:

- Short pin VREG (6) with VDD (7)

- If SPI not used

- Connect all SPI lines to GND → SDO, SDI, CS and CK

- SD pin start-up "network"

- SD pin needs to stay at least 10us at logic low after poweron to leave "safe state"

- Pull-up pin SD (11) to VDD with resistor xx  $k\Omega$  together with coupling to GND with 10nF capacitor

- If driven with +input signal (power switch ON with logic "1")

- Input logic signal tied on IN+ (9); pin IN-/DIAG2 (8) to GND

- If drive with -input signal (power switch ON with logic "0")

- Input logic signal tied on IN-/DIAG2 (8); pin IN+ (9) to VDD

- If DESAT protection activated, pin DIAG1 is latched to GND

- If DESAT protection unused (default V<sub>DESAT</sub>th=7V;  $I_{DESAT}$ =250µA)

- Connect DESAT (18) pin to GNDISO

Basic configuration helps designers to bridge the time to **STGAP2S** (gapLITE)

#### Half-bridge connection example 17

Negative power supply VL for driver section is optional

#### STGAP1S competition comparison table 18

| High power capab                 | oility                                  |       |       |      |       |       |      |

|----------------------------------|-----------------------------------------|-------|-------|------|-------|-------|------|

| Part / Featur                    | STGAP1S                                 | А     | В     | С    | D     | E     | F    |

| I gate @ 25°C [A]                | 5                                       | 2.5   | 2.5   | 4    | 2.5   | 2     | 6    |

| V gate + [V]                     | 36                                      | 30    | 30    | 30   | 30    | 20    | 40   |

| V gate – [V]                     | -10                                     | -15   | -15   | x    | -15   | -12   | X    |

| Desaturation                     | ✓                                       | 1     | ✓     | X    | ✓     | ✓     | X    |

| Soft turn-off                    | ✓ 2LTO<br>Bettor p <mark>erform.</mark> | ~     | ~     | x    | ×     | x     | X    |

| Reliability                      |                                         | X     | 1     | X    | X     | ✓     | 1    |

| Current sense                    |                                         | X     | X     | X    | X     | x     | X    |

| V <sub>CE</sub> Clamp            |                                         | X     | X     | X    | X     | X     | X    |

| Diagnostic                       | 2 pins + SPI                            | ✓     | ✓     | X    | ✓     | ✓     | X    |

| SPI Interface                    | 1 1                                     | x     | x     | x    | x     | x     | x    |

| Max working insulation volt. [V] | 1500                                    | 1230  | 1230  | 1414 | 680   | 1200  | 1200 |

| Real-time                        | SO24W                                   | SO16W | SO16W | SO8W | SO16W | SO16W | SO8W |

| application con                  | l l'Ol                                  |       |       |      |       |       |      |

#### Main application topologies

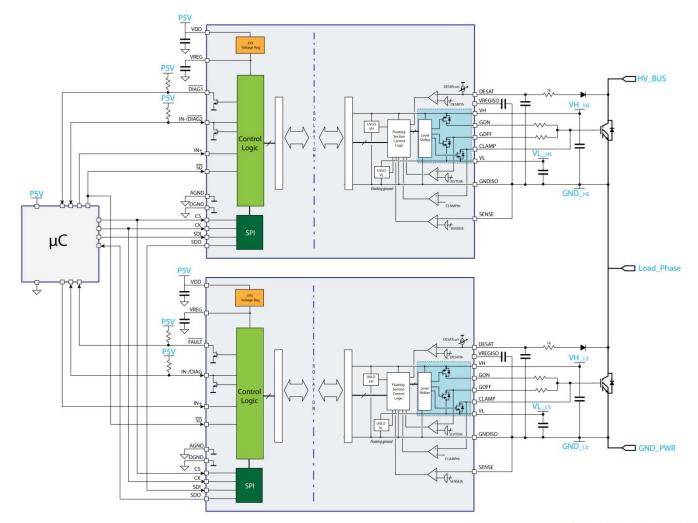

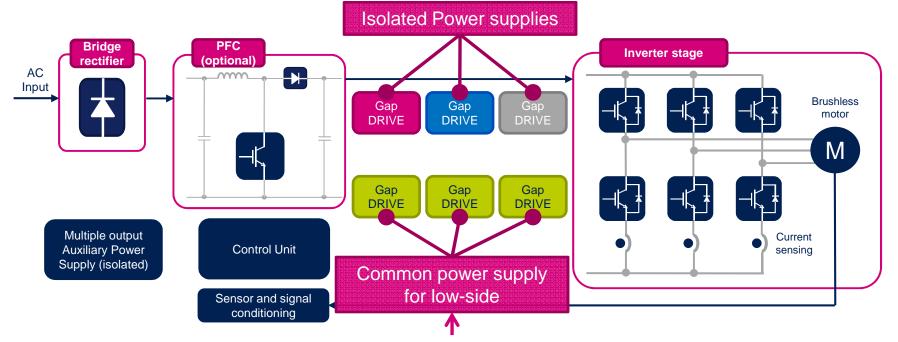

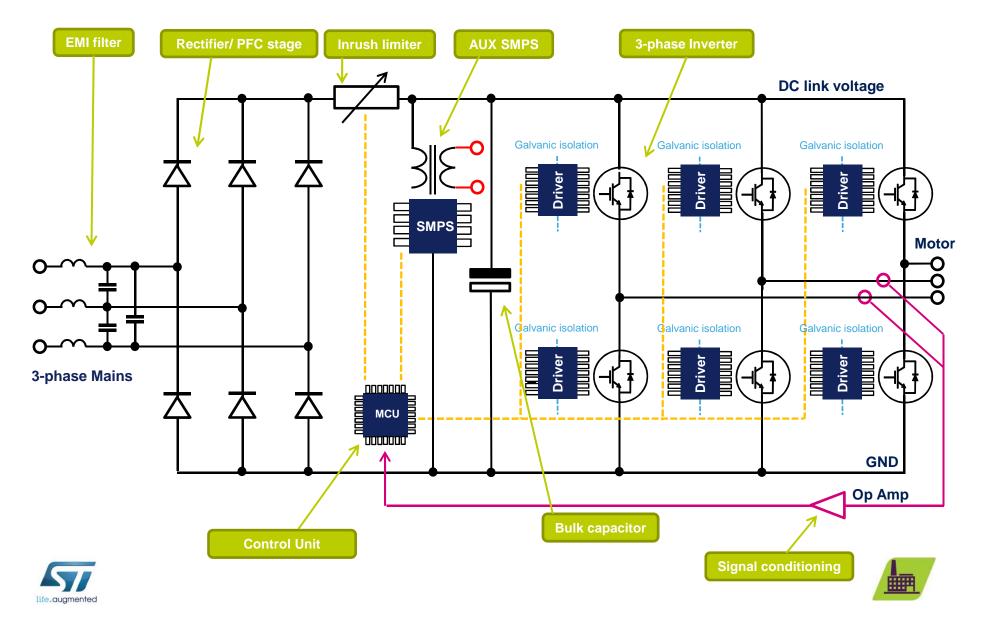

#### 3-phase Inverter for Brushless Motors 20

#### Why isolated drivers even on the low-side?

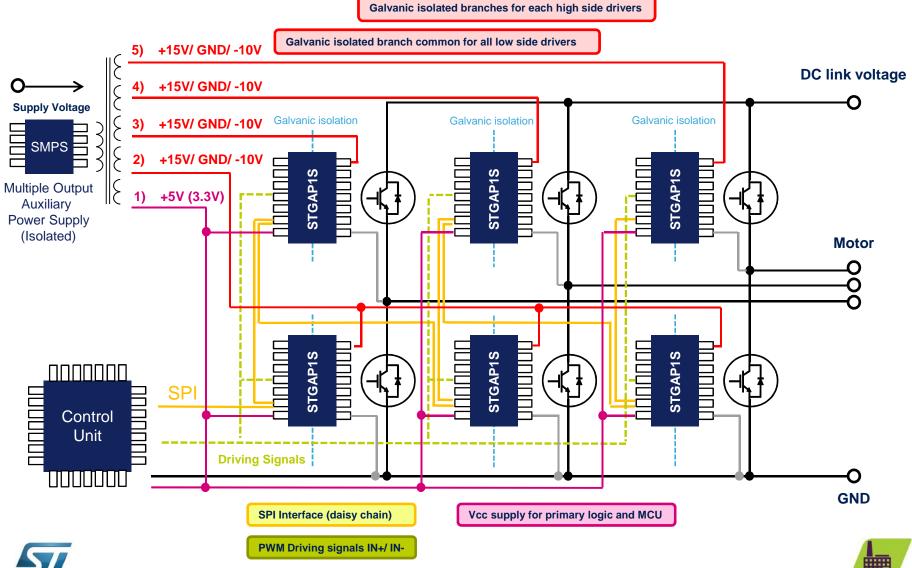

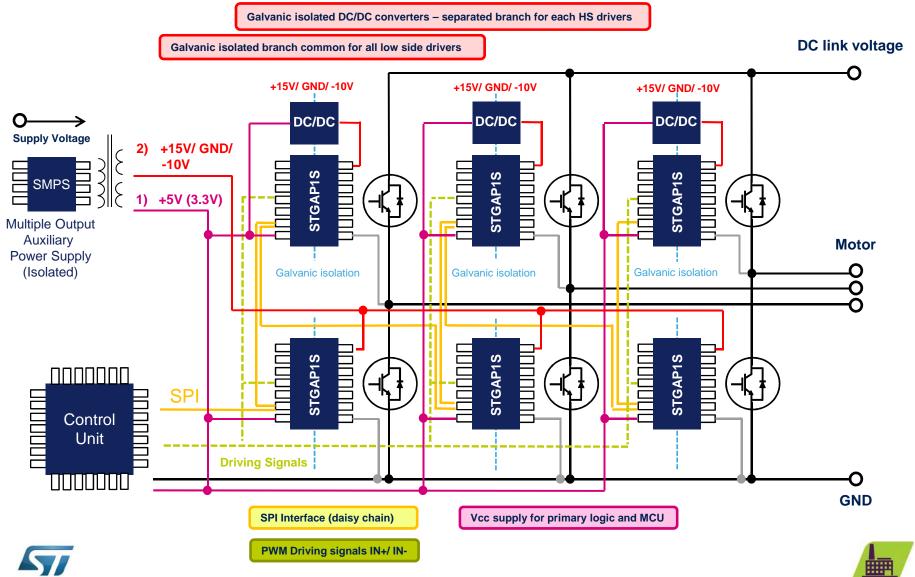

- 6 STGAP1S in total

- 3-phase inverter with Power Module or discrete IGBTs (Trench Field Stop Technology):

- 600 V IGBTs with voltage bus around 300-350 VDC (Trench Gate Field Stop STGxnnH60F Series)

- 1200 V IGBTs with voltage bus around 720-800 VDC (Trench Gate Field Stop STGxnnM120DF3 Series)

- Isolated power supply with multiple outputs:

- Usually Fly-back with 4 outputs: 1 common for low-side Drivers + 1 for each high-side Driver

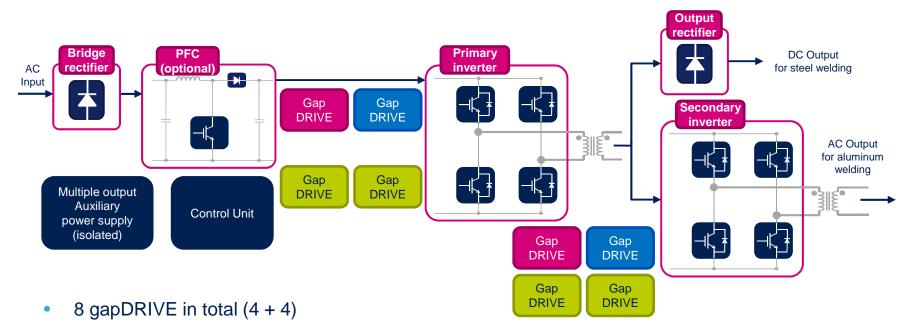

#### Welding: Full-Bridge topology 21

- Welding, full-bridge topology for single and phase-to-phase inverters with discrete IGBTs:

- 600 V IGBTs with voltage bus around 300-350 VDC

- 1200 V IGBT with voltage bus around 720-800 VDC

- Isolated power supply with multiple outputs:

- Usually Fly-back with 3 outputs: 1 common for low-side Drivers + 1 for each high-side Driver

- Secondary inverter needs <u>additional</u> isolated power supply

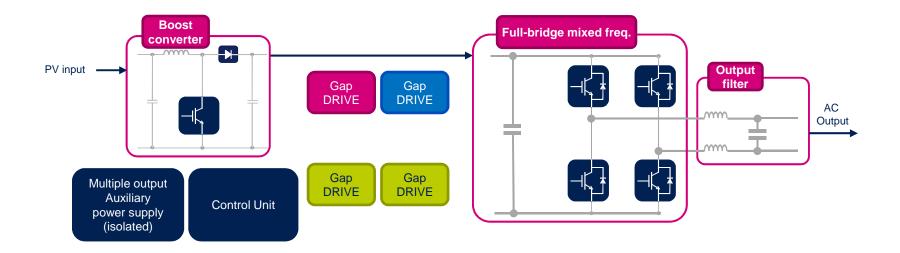

#### Solar Full-Bridge Mixed Frequency Converter 22

- 4 gapDRIVE in total

- Solar full-bridge mixed frequency converter:

- 600 V IGBTs with voltage bus around 300-350 VDC

- 1200 V IGBT with voltage bus around 720-800 VDC

- Isolated power supply with multiple outputs:

- Usually Fly-back with 3 outputs: 1 common for low-side Drivers + 1 for each high-side Driver

#### Connecting STGAP1S 3-phase Motor Control example

#### 3-phase Motor Control Inverter 24

#### gapDRIVE in a 3-phase inverter 25

life.augmented

#### gapDRIVE in a 3-phase inverter 26

life.augmented

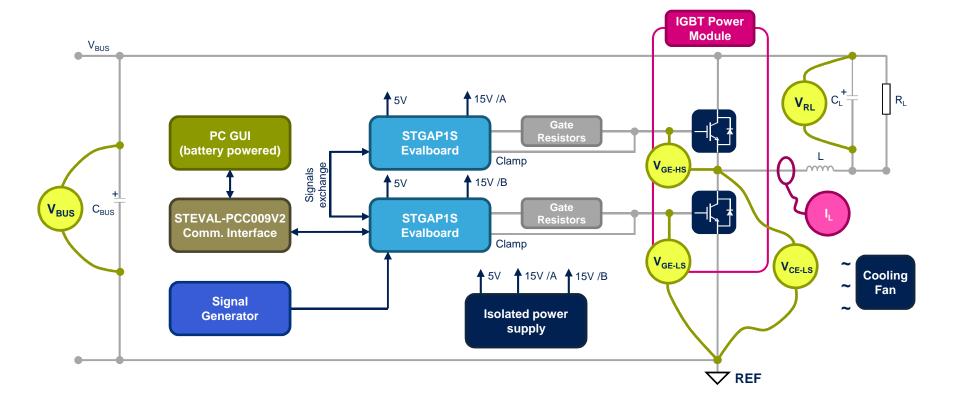

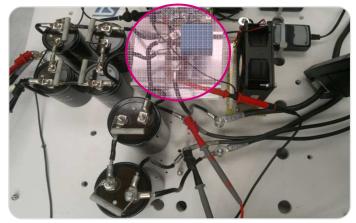

#### Application test at Czech University Driving a 60 kW inductive load

#### Cooperation with Czech University in Prague 28

- Test capabilities in real environment:

- Test of STGAP1S with IGBT module and inductive load:

- Measure the performance of driving capability

- Test set-up, key features:

- 1200 V, 150 A IGBT power module

- 5 kHz switching frequency, 50% duty-cycle

- 2x modified EVALgapDRIVE evaluation boards

- High C capacitors (2200 µF, 450 VDC each), for DC-BUS

- HV power supply 720 VDC, 80 A, ~60kW total power

- LV isolated power supply 5 V and 15 V DC

- About 60kW inductive load for motor simulation

- Power System designed by ST

- Generator and load provided by Czech Technical University

Test set-up, Laboratory of Motor Driving, CVUT

Load inductor (100kg), load resistor (wall closet)

#### System set-up: simplified block diagram

- PC GUI Interface to control STGAP1S evaluation boards through USB/SPI

- 1200 V, 150 A IGBT Module to drive inductive load (L = 1 mH, 300 A /  $R_L$  = 4.8  $\Omega$ , 100 kW)

29

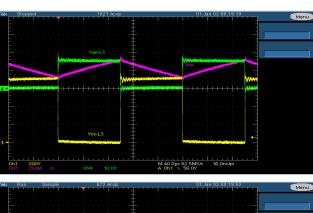

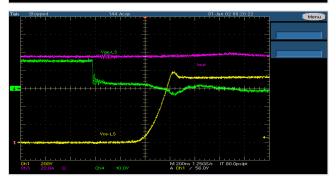

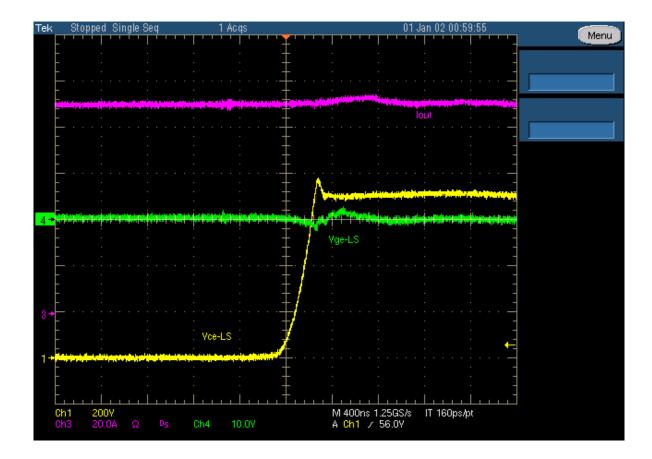

#### Scope waveforms 30

#### Switching at full power:

#### **Test conditions:**

| • | Input voltage                | V <sub>BUS</sub> | 720 VDC    |

|---|------------------------------|------------------|------------|

| • | Output current               | lout             | 80 A RMS   |

| • | Switching frequency          | f <sub>SW</sub>  | 5 kHz, 50% |

| • | Load resistor                | RL               | 4.8 Ω      |

| • | Gate resistor                | R <sub>g</sub>   | 1.4 Ω      |

| • | Driver negative power supply | VL               | 0 V        |

|   |                              |                  |            |

#### Signals:

- Low-side gate voltage Vge-LS •

- Low-side IGBT voltage •

- Half-bridge output current lout •

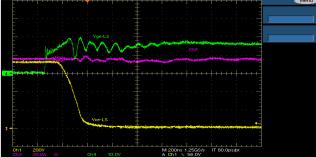

#### Scope waveforms:

- Low-side IGBT turn-on and turn-off (40µs/div) •

- Low-side IGBT turn-on (magnified, 200ns/div)) •

- Low-side IGBT turn-off (magnified, 200ns/div) •

| 720 VDC               |

|-----------------------|

| 80 A RMS              |

| 5 kHz, 50% duty-cycle |

| 4.8 Ω                 |

| 1.4 Ω                 |

| 0 V                   |

|                       |

Green

Yellow

Purple

Vce-LS

#### Miller clamp test result 31

The gate signal of the low-side IGBT is flat, and no induced turn-on phenomenon is observed.

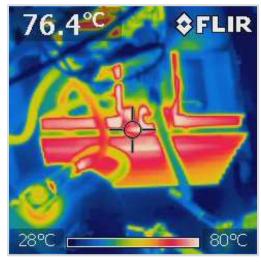

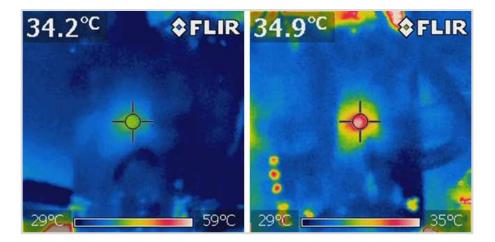

#### Thermal camera snapshots 32

**IGBT** Module

High-side and Low-side drivers

#### STGAP1S test results 33

#### Test results:

- Test performed has shown the ability of driving a 1200 V, 150 A IGBT power module connected to an inductive load

- The highest power reached was met at 720 VDC, 80 A RMS

- STGAP1S driving capabilities limits have not been reached:

- Tested several gate resistors, from 10  $\Omega$  down to 1.4  $\Omega$

- Negative supply voltage VL = 0 V

- No external push-pull transistors on gate pins

- No external transistor on (Miller) clamp pin

- STGAP1S recommended for motor drive applications:

- Up to1200 V, 150 A <u>without</u> external components

- Above 150 A with external transistors and negative VL

Complete 20-page test report available on ERIS/BeST

Test set-up, laboratory of Motor Driving, Czech University

Power System with 1200 V, 150 A IGBT module

#### Evaluation boards & tools IPD technical support

#### **Documentation, Tools and Technical Support**

- How to ease time to market:

- Documentation:

- Main page on st.com: <u>STGAP1S</u>

- Technical report: testing gapDRIVE capabilities (ERIS/BeST)

- Evaluation boards:

- Plug-and-play demonstration board: EVALSTGAP1S

- PC Communication Interface: <u>STEVAL-PCC009V2</u>

- Graphical User Interface (GUI):

- Available on the web: <u>STSW-STGAP001</u>

- Technical Support provided by Prague's Team:

- Send your request to: <a href="mailto:ipd-support-emea@st.com">ipd-support-emea@st.com</a>

EVALSTGAP1S Demonstration Board

STEVAL-PCC009V2 Communication Interface

35

# life.augmented

www.st.com www.st.com/gapdrive