#### High-performance Cortex<sup>™</sup>-M4 MCU

The STM32 F4 series brings to the market the world's highest performance Cortex<sup>™</sup>-M microcontrollers 168 MHz F<sub>CPU</sub>/210 DMIPS 363 Coremark score

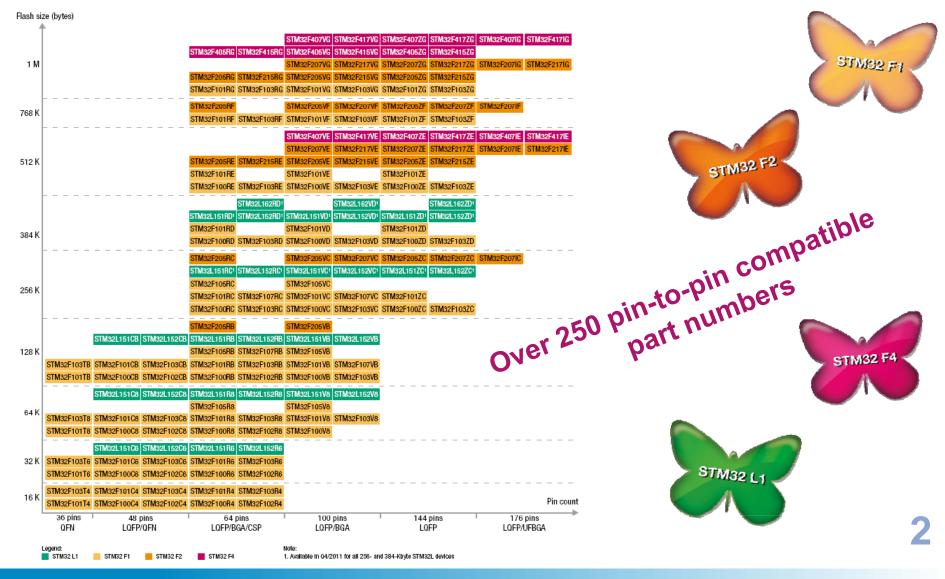

The STM32 F4 series extends the STM32 portfolio 250+ compatible devices already in production, including the F1 series, F2 series and ultra-low-power L1 series

**The STM32 F4 series** reinforces ST's current leadership in Cortex-M microcontrollers, with 45% world market share by units in (2010 or cumulated 2007 to Q1/11) according to ARM reporting

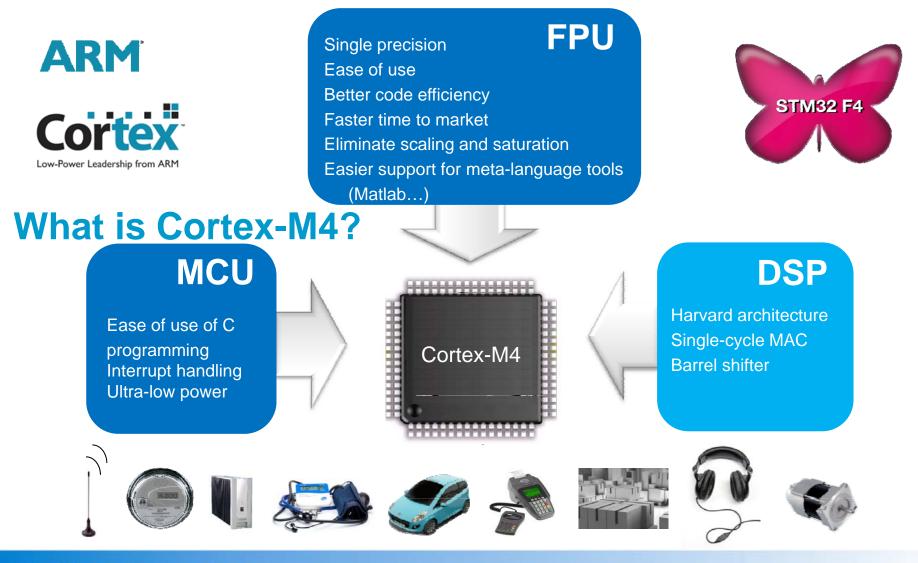

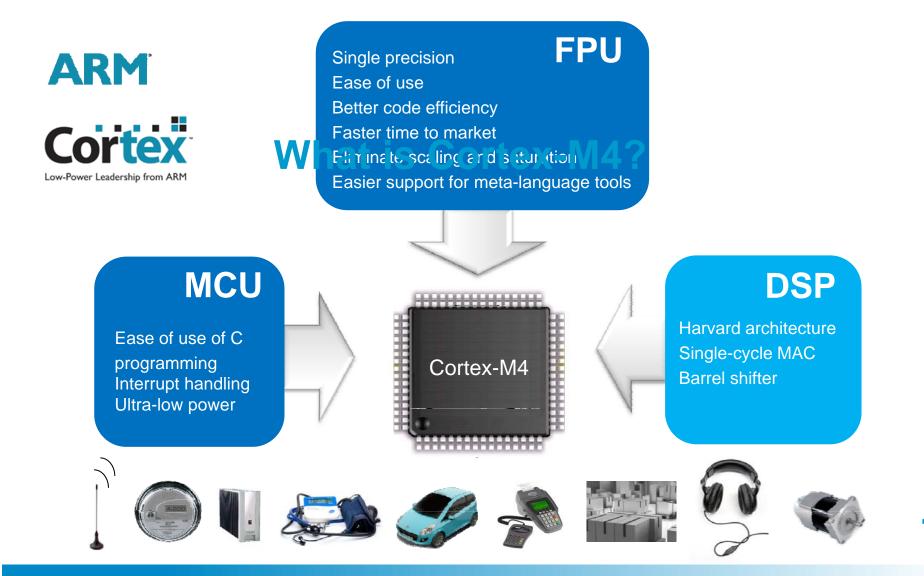

## STM32 F4 series High-performance digital signal controller

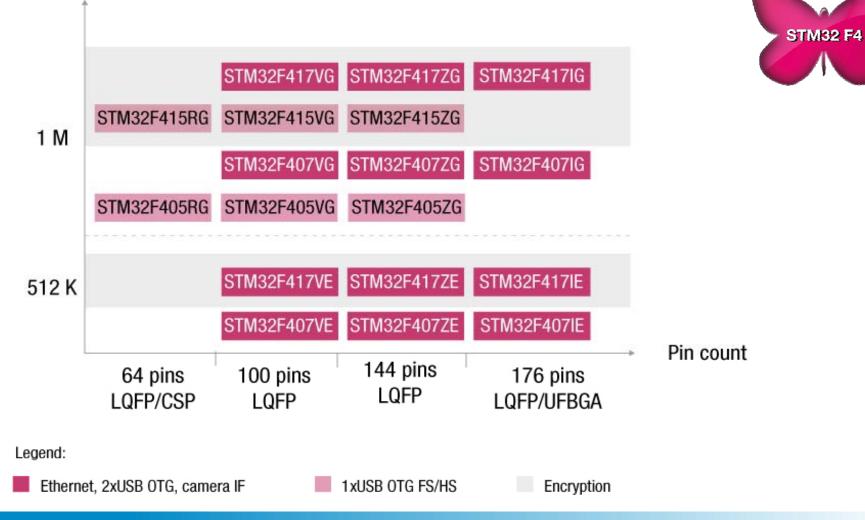

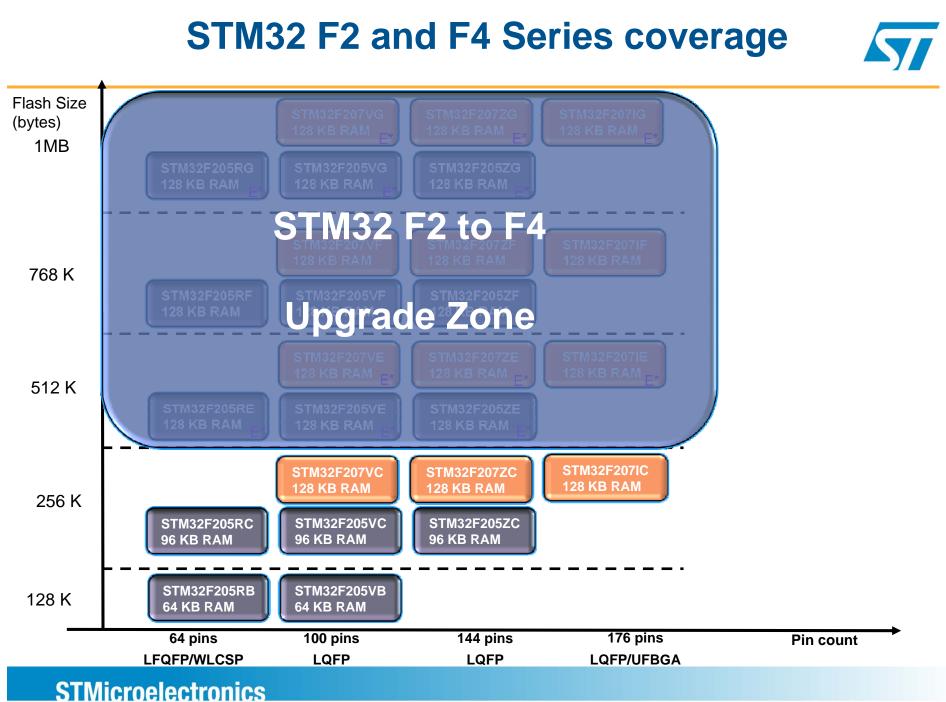

- ST is introducing STM32 products based on Cortex M4 core. Over 30 new part numbers pin-to-pin and software compatible with existing <u>STM32 F2 Series.</u>

- The new DSP and FPU instructions combined to 168Mhz performance open the door to a new level of Digital Signal Controller applications and faster development time.

- STM32 Releasing your creativity

#### Advanced technology and process from ST:

- Memory accelerator: ART Accelerator™

- Multi AHB Bus Matrix

- 90nm process

#### Outstanding results:

- 210DMIPS at 168Mhz.

- Execution from Flash equivalent to 0-wait state performance up to 168Mhz thanks to ST ART Accelerator

#### More Memory

- Up to 1MB Flash,

- 192kB SRAM: 128kB on bus matrix + 64kB on data bus dedicated to the CPU usage

#### Advanced peripherals shared with STM32 F2 Series

- USB OTG High speed 480Mbit/s

- Ethernet MAC 10/100 with IEEE1588

- PWM High speed timers: Now 168Mhz max frequency!

- Crypo/hash processor, 32-bit random number generator (RNG)

- 32-bit RTC with calendar: Now with sub 1 second accuracy, and <1uA typ!</li>

### STM32 F4 Series highlights 4/4

#### Further improvements

- Low voltage: 1.8V to 3.6V VDD, down to 1.7\*V on most packages

- Full duplex I2S peripherals

- 12-bit ADC: 0.41µs conversion/2.4Msps (7.2Msps in interleaved mode)

- High speed USART up to 10.5Mbits/s

- High speed SPI up to 37.5Mbits/s

- Camera interface up to 54MBytes/s

\*external reset circuitry required to support 1.7V

### STM32 F4 series – applications served

- Points of sale/inventory -**Building** management

- Industrial automation and solar panels

- Security/fire/HVAC

**Test and measurement**

- **Transportation**

Medical

Communication

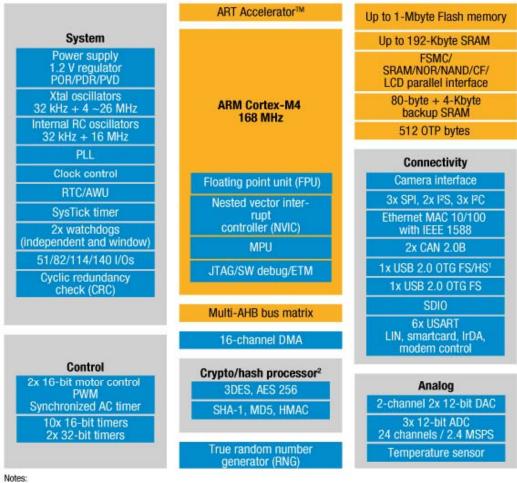

### STM32 F4 block diagram

#### Feature highlight

- 168 MHz Cortex-M4 CPU

- Floating point unit (FPU)

- ART Accelerator TM

- Multi-level AHB bus matrix

- 1-Mbyte Flash, 192-Kbyte SRAM

- 1.7 to 3.6 V supply

- RTC: <1 µA typ, sub second accuracy

- 2x full duplex I<sup>2</sup>S

- 3x 12-bit ADC

0.41 µs/2.4 MSPS

- 168 MHz timers

- 1. HS requires an external PHY connected to the ULPI interface

- 2. Crypto/hash processor on STM32F417 and STM32F415

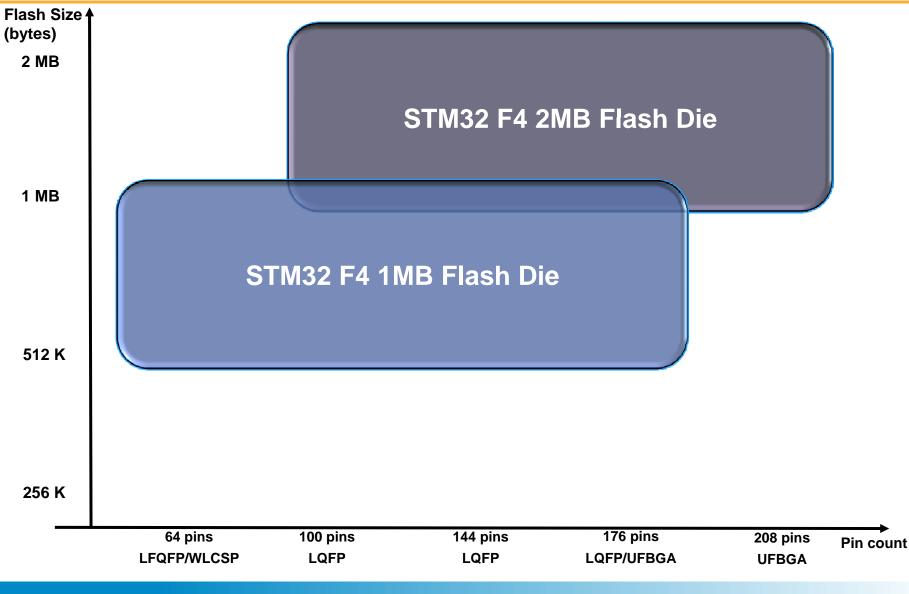

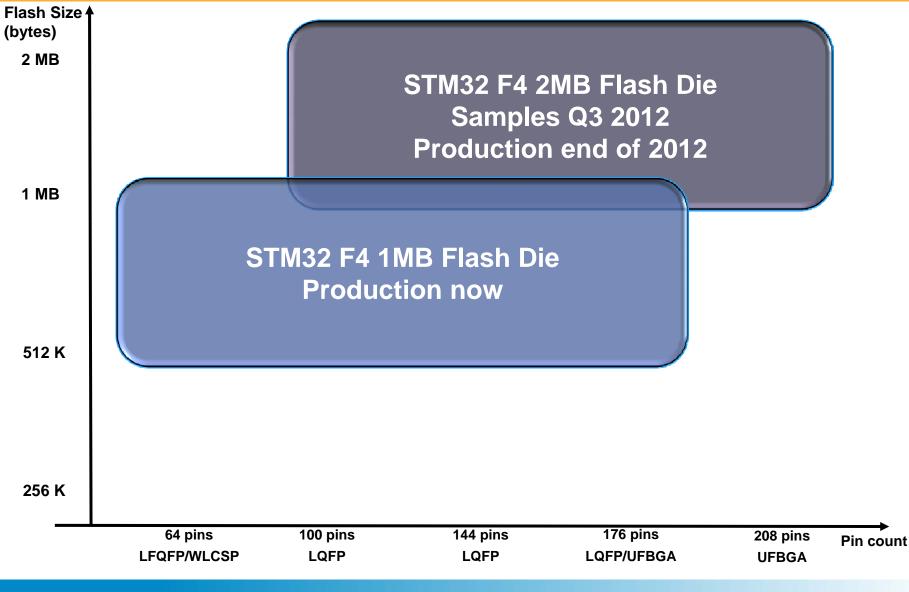

Flash size (bytes)

### **STM32 product series**

#### 4 product series

Common core peripherals and architecture:

| Communication peripherals:<br>USART, SPI, I <sup>2</sup> C             |   | Cortex-M4<br>with DSP<br>and FPU | 1   |

|------------------------------------------------------------------------|---|----------------------------------|-----|

| Multiple general-purpose timers                                        |   | STM32 F2 s                       | eri |

| Integrated reset and brown-out warning                                 |   | 120 MHz<br>Cortex-M3<br>CPU      | 1   |

| Multiple DMA                                                           |   | STM32 F1 s                       | er  |

| 2x watchdogs<br>Real-time clock                                        |   | 72 MHz<br>Cortex-M3              | (   |

| Integrated regulator<br>PLL and clock circuit                          |   | CPU<br>STM32 F1 s                | er  |

| External memory interface (FSMC)                                       |   | 72 MHz                           |     |

| Dual 12-bit DAC                                                        |   | Cortex-M3<br>CPU                 | ç   |

| Up to 3x 12-bit ADC (up to 0.41 µs)                                    |   | STM32 F1 s                       | er  |

| Main oscillator and 32 kHz oscillator                                  |   | 48 MHz                           |     |

| Low-speed and high-speed internal RC<br>oscillators                    | + | Cortex-M3<br>CPU                 |     |

| -40 to +85 °C and up to 105 °C                                         |   | STM32 F1 s                       | er  |

| operating temperature range                                            |   | 36 MHz                           |     |

| Low voltage 2.0 to 3.6 V or<br>1.65/1.7 to 3.6 V (depending on series) |   | Cortex-M3<br>CPU                 | 8   |

| 5.0 V tolerant I/0s                                                    |   | STM32 F1 s                       | er  |

| Temperature sensor                                                     |   | 24 MHz<br>Cortex-M3<br>CPU       |     |

|                                                                        |   |                                  |     |

#### STM32 F4 series - High performance with DSP (STM32F405/415/407/417)

|   | 168 MHz<br>Cortex-M4<br>with DSP<br>and FPU | Up to<br>192-Kbyte<br>SRAM | Up to<br>1-Mbyte<br>Flash   | 2x USB<br>2.0 OTG<br>FS/HS | 3-phase<br>MC timer               | 2x CAN<br>2.0B      | SDIO<br>2x I²S audio<br>Camera IF              | Ethernet<br>IEEE 1588 | Crypto/hash<br>processor<br>and RNG | STM32 F1 |

|---|---------------------------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------------|---------------------|------------------------------------------------|-----------------------|-------------------------------------|----------|

|   | STM32 F2 s                                  | eries - High               | performance                 | (STM32F20                  | 5/215/207/217                     | 1                   |                                                |                       |                                     |          |

|   | 120 MHz<br>Cortex-M3<br>CPU                 | Up to<br>128-Kbyte<br>SRAM | Up to<br>1-Mbyte<br>Flash   | 2x USB<br>2.0 OTG<br>FS/HS | 3-phase<br>MC timer               | 2x CAN<br>2.0B      | SDIO<br>2x I <sup>2</sup> S audio<br>Camera IF | Ethernet<br>IEEE 1588 | Crypto/hash<br>processor<br>and RNG | STMS2 F2 |

|   | STM32 F1 s                                  | eries - Conn               | ectivity line (             | STM32F105                  | /107)                             |                     |                                                |                       |                                     |          |

|   | 72 MHz<br>Cortex-M3<br>CPU                  | Up to<br>64-Kbyte<br>SRAM  | Up to<br>256-Kbyte<br>Flash | USB 2.0<br>OTG FS          | 3-phase<br>MC timer               | 2x CAN<br>2.0B      | 2x I²S audio                                   | Ethernet<br>IEEE 1588 |                                     |          |

|   | STM32 F1 s                                  | eries - Perfo              | rmance line                 | (STM32F103                 | 3)                                |                     |                                                |                       |                                     |          |

|   | 72 MHz<br>Cortex-M3<br>CPU                  | Up to<br>96-Kbyte<br>SRAM  | Up to<br>1-Mbyte<br>Flash   | USB FS<br>device           | 3-phase<br>MC timer               | CAN<br>2.0B         | SDI0<br>2x I²S                                 |                       |                                     |          |

|   | STM32 F1 s                                  | eries - USB /              | Access line (               | STM32F102)                 | )                                 |                     |                                                |                       |                                     |          |

| + | 48 MHz<br>Cortex-M3<br>CPU                  | Up to<br>16-Kbyte<br>SRAM  | Up to<br>128-Kbyte<br>Flash | USB FS<br>device           |                                   |                     |                                                |                       |                                     | STM52 FI |

|   | STM32 F1 s                                  | eries - Acces              | ss line (STM3               | 32F101)                    |                                   |                     |                                                |                       |                                     |          |

|   | 36 MHz<br>Cortex-M3<br>CPU                  | Up to<br>80-Kbyte<br>SRAM  | Up to<br>1-Mbyte<br>Flash   |                            |                                   |                     |                                                |                       |                                     |          |

|   | STM32 F1 s                                  | eries - Value              | line (STM32                 | F100)                      |                                   |                     |                                                |                       |                                     |          |

|   | 24 MHz<br>Cortex-M3<br>CPU                  | Up to<br>32-Kbyte<br>SRAM  | Up to<br>512-Kbyte<br>Flash | 3-phase<br>MC timer        | CEC                               |                     |                                                |                       |                                     |          |

|   | STM32 L1 s                                  | eries - Ultra-             | low-power (                 | STM32F151                  | /152)                             |                     |                                                |                       |                                     |          |

|   | 32 MHz<br>Cortex-M3<br>CPU                  | Up to<br>48-Kbyte<br>SRAM  | Up to<br>384-Kbyte<br>Flash | USB FS<br>device           | Data EEPROM<br>up to<br>12 Kbytes | LCD<br>8x40<br>4x44 | Comparator                                     | BOR<br>MSI<br>VScal   | AES<br>128-bit                      | STM32 L1 |

### STM32 – leading Cortex-M portfolio

# The cheapest and quickest way to discover the STM32F4

- Everything included for a quick start with the STM32F4 serie

- Price: \$ 14.90 (RRP)

- DCPL : \$ 11.90

- Order code: STM32F4DISCOVERY

- Available in ST stock from October 2011

- In circuit ST-LINK/V2 debugger / programmer included to debug Discovery kit applications or other target board applications.

- Dedicated web site <u>www.st.com/stm32F4discovery</u>

- Large number of examples ready to run

- Schematics

- Forums and more

### STM32F4 Discovery Board

- On-board ST-LINK/V2 with selection mode switch to use the kit as stand-alone ST-LINK with SWD connector

- Designed to be powered by USB or by external power 5V or 3.3V supply

- Can supply target application with 5 Volts or 3 Volts

- Two User LEDs (Green and Blue)

- Audio codec

- Mems Micro (MP45DT02)

- One user Push Button

- Extension header for all QFP64 I/Os for quick connection to prototyping board or easy probing

- ST-LINK/V2 SWD connector STM32F407VGT6 User button-Audio Jack

#### September : STM32F4 eval board

- Eval board : STM3240G-EVAL : 21<sup>st</sup> of September

- For any needs before contact your local ST support

- DCPL : \$279

- RRP: \$349

Sample : 21<sup>st</sup> of September

| LQFP100 | STM32F407VGT6 |

|---------|---------------|

| LQFP144 | STM32F457ZGT6 |

| LQFP176 | STM32F457IGT6 |

| BGA176  | STM32F457IGH6 |

| LQFP64  | STM32F455RGT6 |

|         |               |

Full production November 2011

2011

#### Key messages to remember

- STM32 F4 series

- World's highest performance

- Extends the STM32 portfolio to over 250+ compatible devices

- One-in-two Cortex-M MCUs shipped worldwide is an STM32

**Discovery kits available now**

STM32F4DISCOVERY

#### www.st.com/stm32f4

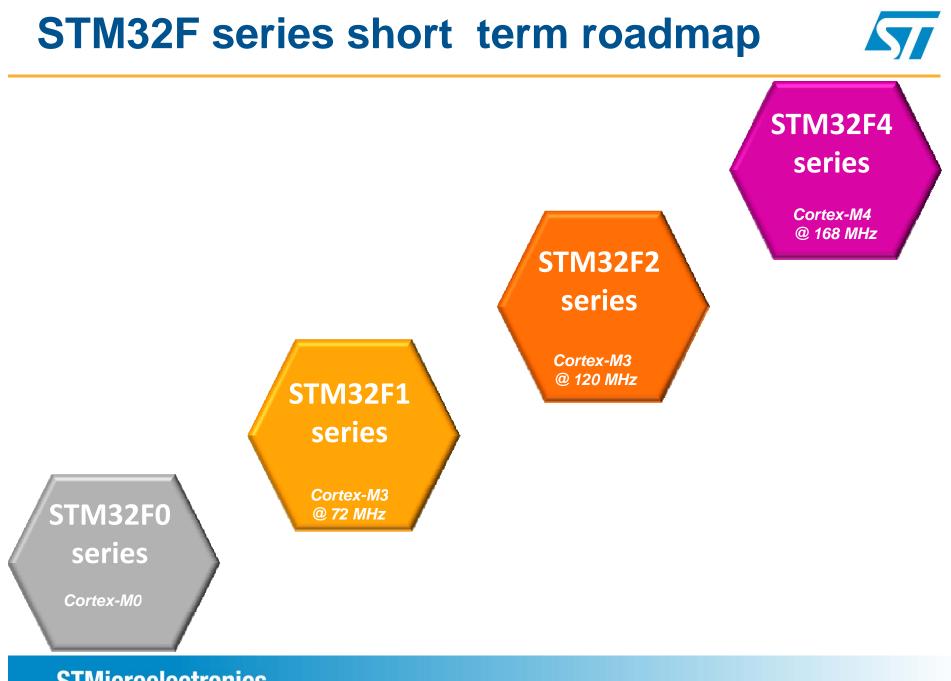

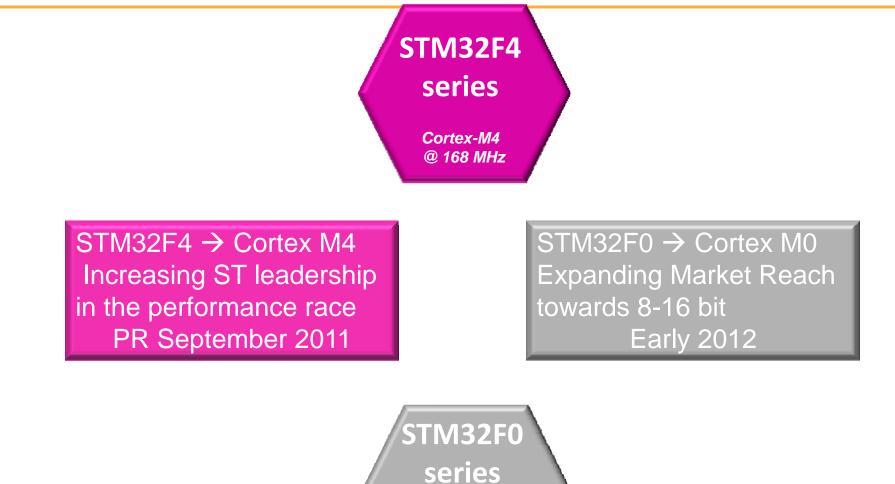

## STM32F roadmap

#### STM32 Next 2 Major Launch

Cortex-M0

#### STM32 F4 Roadmap

#### STM32 F4 Roadmap

## **Backup Slides**

- STM32F4 starter kits from IAR and Keil available in Q4 2011

- Order codes:

- IAR: STM3240G-SK/IAR

- KEIL: STM3240G-SK/KEI

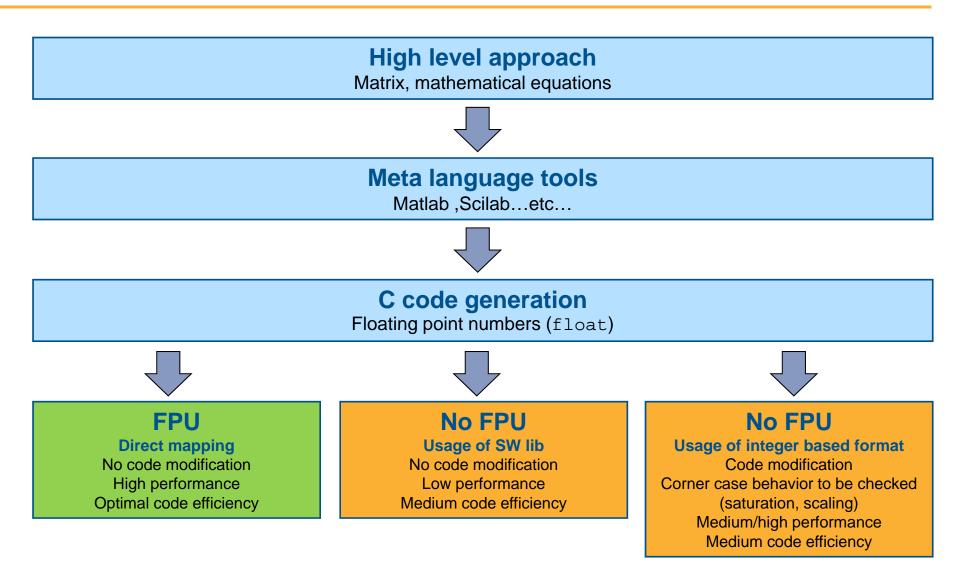

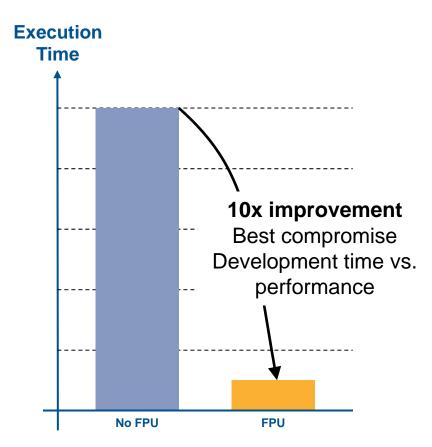

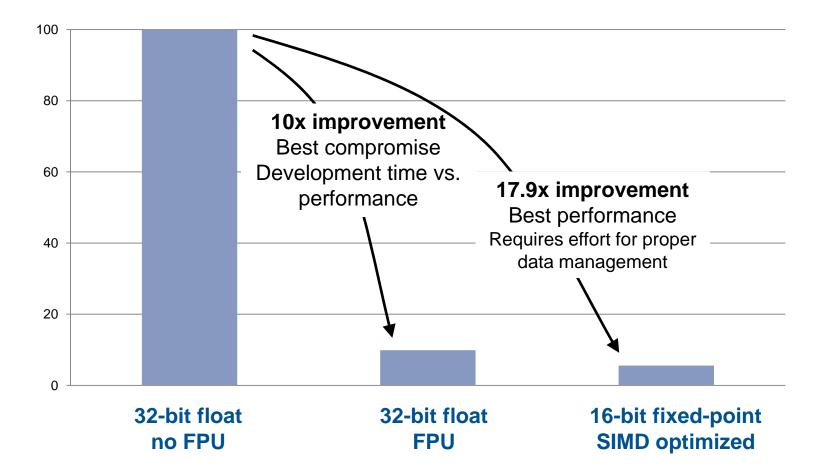

## **FPU benefits and performance**

#### **FPU benefits in real life applications**

Time execution comparison for a 29 coefficient FIR on float 32 with and without FPU (CMSIS library)

## **DSP** benefits and performance

#### Single-cycle multiply-accumulate (MAC)

- The multiplier unit allows any MUL or MAC instructions to be executed in a single cycle

- Signed/Unsigned Multiply

- Signed/Unsigned Multiply-Accumulate

- Signed/Unsigned Multiply-Accumulate Long (64-bit)

- Benefits : Speed improvement vs. Cortex-M3

- 4x for 16-bit MAC (dual 16-bit MAC)

- 2x for 32-bit MAC

- up to 7x for 64-bit MAC

• **FIR filter** execution time (CMSIS library)

## **ARM Cortex M4 in few words**

#### **Cortex-M processors**

- Forget traditional 8/16/32-bit classifications

- Seamless architecture across all applications

- Every product optimised for ultra low power and ease of use

| Cortex-M0               | Cortex-M3                | Cortex-M4                 |

|-------------------------|--------------------------|---------------------------|

| "8/16-bit" applications | "16/32-bit" applications | "32-bit/DSC" applications |

|                         |                          |                           |

#### **Binary and tool compatible**

## Cortex-M processors binary compatible

| РКН    | QADD        | QADD16 QADD8       | GASX     | QDADD    | QDSUB    | QSAX    | QSUB       |

|--------|-------------|--------------------|----------|----------|----------|---------|------------|

| QSUB16 | QSUB8       | SADD16 SADD8       | SASX     | SEL      | SHADD16  | SHADD8  | SHASX      |

| SHSAX  | SHSUB16     | SHSUB8 SMLAB       | B SMLABT | SMLATB   | SMLATT   | SMLAD   | SMLALBB    |

|        |             |                    |          |          |          | SMLALBT | SMLALTB    |

| ADC    | ADD         | ADR AND            | ASR      | В        | CLZ      | SMLALTT | SMLALD     |

| BFC    | BFI         | BIC CDP            | CLREX    | CBNZ CBZ | CMN      | SMLAWB  | SMLAWT     |

| СМР    |             |                    | DBG      | EOR      | LDC      | SMLSD   | SMLSLD     |

| LDMIA  | BKPT BLX    | ADC ADD ADR        | LDMDB    | LDR      | LDRB     | SMMLA   | SMMLS      |

| LDRBT  | BX CPS      | AND ASR B          | LDRD     | LDREX    | LDREXB   | SMMUL   | SMUAD      |

| LDREXH | DMB         | BL BIC             | LDRH     | LDRHT    | LDRSB    | SMULBB  | SMULBT     |

| LDRSBT | DSB         | CMN CMP EOR        | LDRSHT   | LDRSH    | LDRT     | SMULTB  | SMULTT     |

| MCR    | ISB         | LDR LDRB LDM       | LSL      | LSR      | MLS      | SMULWB  | SMULWT     |

| MCRR   | MRS         | LDRH LDRSB (LDRSH) | MLA      | MOV      | MOVT     | SMUSD   | SSAT16     |

| MRC    | MSR         | LSL LSR MOV        | MRRC     | MUL      | MVN      | SSAX    | SSUB16     |

| NOP    | NOP REV     | MUL MVN ORR        | ORN      | ORR      | PLD      | SSUB8   | SXTAB      |

| PLDW   | REV16 REVSH | POP (PUSH) (ROR    | PLI      | РОР      | PUSH     | SXTAB16 | SXTAH      |

| RBIT   | SEV SXTB    | RSB SBC STM        | REV      | REV16    | REVSH    | SXTB16  | UADD16     |

| ROR    | SXTH UXTB   | STR STRB STRH      | RRX      | RSB      | SBC      | UADD8   | UASX       |

| SBFX   | UXTH WFE    | SUB SVC TST        | SDIV     | SEV      | SMLAL    | UHADD16 | UHADD8     |

| SMULL  | WFI YIELD   | CORTEX-M0/M1       | SSAT     | STC      | STMIA    | UHASX   | UHSAX      |

| STMDB  |             |                    |          | STRB     | STRBT    | UHSUB16 | UHSUB8     |

| STRD   | STREX       | STREXB STREXH      | STRH     | STRHT    | STRT     | UMAAL   | UQADD16    |

| SUB    | SXTB        | SXTH TBB           | ТВН      | TEQ      | TST      | UQADD8  | UQASX      |

| UBFX   |             | UMLAL UMULL        | USAT     | UXTB     | UXTH     | UQSAX   | UQSUB16    |

| WFE    | WFI         | YIELD IT           |          | C        | ORTEX-M3 | UQSUB8  | USAD8      |

|        |             |                    |          |          |          | USADA8  | USAT16     |

| USAX   | USUB16      | USUB8 UXTAB        | UXTAB16  | UXTAH    | UXTB16   |         | Cortex-M4  |

| L      |             |                    |          |          |          |         |            |

| VABS   | VADD        |                    |          |          |          |         | VLDR       |

| VMLA   | VMLS        |                    | VMSR     |          | VNEG     |         | VNMLS      |

| VNMUL  | VPOP        | VPUSH VSQRT        |          |          |          | )       | Cortex-M4F |

|        |             |                    |          |          |          |         |            |

**STMicroelectronics**

Low-Power Leadership from ARM

#### **ARM Cortex M4 Core**

### **Cortex-M feature set comparison**

|                               | Cortex-M0                             | Cortex-M3       | Cortex-M4                         |

|-------------------------------|---------------------------------------|-----------------|-----------------------------------|

| Architecture Version          | V6M                                   | v7M             | v7ME                              |

| Instruction set architecture  | Thumb, Thumb-2<br>System Instructions | Thumb + Thumb-2 | Thumb + Thumb-2,<br>DSP, SIMD, FP |

| DMIPS/MHz                     | 0.9                                   | 1.25            | 1.25                              |

| Bus interfaces                | 1                                     | 3               | 3                                 |

| Integrated NVIC               | Yes                                   | Yes             | Yes                               |

| Number interrupts             | 1-32 + NMI                            | 1-240 + NMI     | 1-240 + NMI                       |

| Interrupt priorities          | 4                                     | 8-256           | 8-256                             |

| Breakpoints, Watchpoints      | 4/2/0, 2/1/0                          | 8/4/0, 2/1/0    | 8/4/0, 2/1/0                      |

| Memory Protection Unit (MPU)  | No                                    | Yes (Option)    | Yes (Option)                      |

| Integrated trace option (ETM) | No                                    | Yes (Option)    | Yes (Option)                      |

| Fault Robust Interface        | No                                    | Yes (Option)    | No                                |

| Single Cycle Multiply         | Yes (Option)                          | Yes             | Yes                               |

| Hardware Divide               | No                                    | Yes             | Yes                               |

| WIC Support                   | Yes                                   | Yes             | Yes                               |

| Bit banding support           | No                                    | Yes             | Yes                               |

| Single cycle DSP/SIMD         | No                                    | No              | Yes                               |

| Floating point hardware       | No                                    | No              | Yes                               |

| Bus protocol                  | AHB Lite                              | AHB Lite, APB   | AHB Lite, APB                     |

| CMSIS Support                 | Yes                                   | Yes             | Yes                               |

Low-Power Leadership from 36RM

## **DSP lib provided for free by ARM**

- The benefits of software libraries for Cortex-M4

- Enables end user to develop applications faster

- Keeps end user abstracted from low level programming

- Benchmarking vehicle during system development

- Clear competitive positioning against incumbent DSP/DSC offerings

- Accelerate third party software development

- Keeping it easy to access for end user

- Minimal entry barrier very easy to access and use

- One standard library no duplicated efforts

- ARM channels effort/resources with software partner

- Value add through another level of software eg: filter config tools

## **DSP lib function list snapshot**

- Basic math vector mathematics

- Fast math sin, cos, sqrt etc

- Interpolation linear, bilinear

- Complex math

- Statistics max, min, RMS etc

- Filtering IIR, FIR, LMS etc

- Transforms FFT(real and complex), Cosine transform etc

- Matrix functions

- PID Controller

- Support functions copy/fill arrays, data type conversions etc

## STM32 F4 vs. STM32 F2

**STMicroelectronics**

#### **Differences in Core and System Architecture**

|                            | STM32 F2                                                                     | STM32 F4                                                                                                          |

|----------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Core                       | ARM Cortex M3 (r2p0)                                                         | ARM Cortex M4F * (r0p1)                                                                                           |

| Floating point calculation | s/w                                                                          | Single precision h/w                                                                                              |

| Performance / with ART ON  | "0ws like" performance<br>thanks to ART<br>Accelerator:<br>120MHz:1.65V-3.6V | "Ows like" performance thanks to<br>ART Accelerator:<br>168Mhz: 2.1V–3.6V<br>144MHz:1.8V–2.1V<br>128MHz:1.7V–1.8V |

| SRAM internal capacity     | 128KB of system<br>memory                                                    | 192KB (128KB system<br>memory + 64KB dedicated to<br>CPU data)                                                    |

#### **Differences in Core and System Architecture**

|                                                                          | STM32 F2                                                                              | STM32 F4                                                                      |

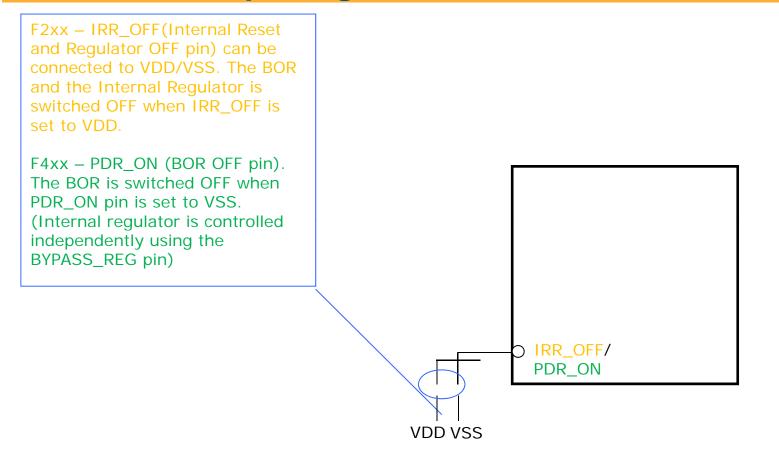

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Internal Regulator Bypass                                                | Available only on WLCSP64<br>(IRR_OFF pin) and BGA176<br>(BYPASS_REG pin)<br>packages | Available only on WLCSP64 and<br>BGA176 (BYPASS_REG pin)<br>packages          |

|                                                                          | On WLCSP64 this<br>functionality can not be<br>dissociated from BOR OFF               | BOR OFF and Internal regulator bypass are non exclusive on the above packages |

| VDD min extension from 1.8V down<br>to<br>1.65V (requires BOR OFF) on F2 | Available only on WLCSP64 package (IRR_OFF pin)                                       | Available on all packages (PDR_ON pin) except on LQFP64 pin package           |

| 1.7V (requires BOR OFF) on F4                                            | This functionality can not be dissociated from Regulator bypass                       | This functionality can be dissociated from Regulator bypass                   |

| Voltage Scaling (Internal regulator output)                              | None                                                                                  | Performance Optimization (150 MHz<br>max)<br>Power Optimization (120MHz max)  |

#### **Differences in Peripheral System Architecture**

|                     | STM32 F2                                                                                              | STM32 F4                                                                                    |

|---------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| FSMC (improvements) | Remap capability on<br>bank1-NE1/NE2, but<br>no capability to<br>access other banks<br>while remapped | Remap capability on<br>bank1-NE1/NE2, with<br>access to other FSMC<br>banks while remapped. |

| I2S                 | 2x I2S Half duplex                                                                                    | 2x I2S Full duplex.                                                                         |

#### **New RTC implementation**

|                                              | STM32 F2                                | STM32 F4                                                              |

|----------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------|

| Calendar Sub seconds access                  | NO                                      | YES (resolution down to RTC clock)                                    |

| Calendar resolution                          | From RTCCLK/2 to<br>RTCCLK/2^20         | From RTCCLK/1 to<br>RTCCLK/2^22                                       |

| Calendar read and synchronization on the fly | NO                                      | YES                                                                   |

| Alarm on calendar                            | 2 alarms<br>Sec, Min, Hour,<br>Date/day | 2 alarms<br>Sec, Min, Hour,<br>Date/day, <b>Sub</b><br><b>seconds</b> |

|                         | STM32 F2                                                                                                       | STM32 F4                                                                                                           |

|-------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Calendar<br>Calibration | Calib window : <b>64min</b><br>Calibration step:<br>Negative:-2ppm<br>Positive: +4ppm<br>Range [-63ppm+126ppm] | Calib window : <b>8s/16s/32s</b><br>Calibration step:<br>Negative or Positive:<br>3.81ppm/1.91ppm/ <b>0.95 ppm</b> |

|                         |                                                                                                                | Range [-480ppm +480ppm]                                                                                            |

| Timestamp               | YES<br>Sec, Min, Hour, Date                                                                                    | YES<br>Sec, Min, Hour, Date, <b>Sub</b><br><b>seconds</b>                                                          |

| Tamper                  | YES (2 pins /1 event)<br>Edge Detection only                                                                   | YES (2 pins/ 2 events)<br>Level Detection with<br>Configurable filtering                                           |

#### Compatible board design for LQFP100-144-176 and BGA 176 packages

# Compatible board design for WLCSP64+2 package

#### www.st.com/stm32f4

**STMicroelectronics**

### Glossary

- ART Accelerator <sup>™</sup> : ST's adaptive real-time accelerator

- CMSIS: Cortex<sup>™</sup> microcontroller software interface standard

- MCU: microcontroller unit

- DSC: digital signal controller

- DSP: digital signal processor

- FPU: floating point unit

- RTC: real-time clock

- MPU: memory protection unit

- FSMC: flexible static memory controller