Volume 1, Issue 1

Volume 1, Issue 1

#### **Table of Contents**

- 2 Editorial

- 3 Selecting the Optimal MCU for Your Embedded Application

- 12 Maximizing

Performance

for Real-Time

Embedded

Systems

- 20 Designing for Low Power Applications

- 27 Simplifying

Embedded Design

for Accelerated

Time-to-Market

- 35 Designing Efficient Connectivity

- 42 Accelerating

Next-Generation

Design Through

IP Reuse

## Navigating Next-Generation Design

By Nicholas Cravotta, Technical Editor

A great deal has changed in the thirty years I've designed and written about embedded systems. When I started, writing code was a straightforward, linear process. You told the CPU to do something, and then you waited until it was done.

Over the years, I've watched as the MCU has evolved from a simple CPU to an efficient network of integrated processors working in parallel. Each accelerator or coprocessor operates independently of the CPU, enabling the simultaneous processing of an incredible amount of data. In an MCU like the new STM32 F4 from ST. these integrated processors are combined with a multi-layer bus interconnect and multiple DMA engines to provide tremendous processing capacity.

Development tools have evolved as well. Today developers can profile application code non-intrusively to focus their optimization efforts. Similarly, they can accurately measure power consumption while an MCU is switching between active and low power modes, even to the point of showing developers

which line of code is responsible for a spike in power consumption.

You can see the results of this evolution in designs like the Stanford Xenith solar vehicle shown on the cover of this issue. Stanford selected the STM32 for several of its more complex subsystems because of the architecture's extensive peripheral set and performance. In addition, the team found that STM32 MCUs are so energy efficient that there is virtually no operating cost in terms of power to using them. The integrated development environment also makes it easy for new team members to immediately begin contributing.

For example, a single STM32107RB monitors the voltage of the Xenith's 35 cell groups, measures the temperature and current, and performs critical operations such as controlling the flow of power through the vehicle. Four STM32F205RBT6s track the maximum power point of the solar array to optimize power density and efficiency. This process involves synchronous rectification which requires accurate interrupt

handling and FET switching at very specific times. Two STM32107RBs manage communication between the driver, the vehicle, the motor controller, and the rear wheel steering system; they also accurately read encoders with minimal overhead. Several STM32F103C8T6s are used to manage ancillary systems such as lighting, telemetry, and tirepressure monitoring. You can see the Xenith in action here.

We live in a fast-changing world, and the only way to keep up is to find silicon and tools that evolve as quickly. As you can see with the Stanford solar vehicle, a single architecture like the STM32 is versatile enough to serve across many diverse applications using the same toolset. This is no accident.

In this issue, we'll explore the current state-of-art in designing embedded systems. Whether you're interested in optimizing performance, minimizing power, connecting to the network, or designing for reuse, you'll find it here.

Enjoy! 😽

# Selecting the Optimal MCU for Your Embedded Application

By Alec Bath, Applications Engineer, STMicroelectronics

Innovation in silicon technology has escalated over the past decade with the availability of MCUs which combine a powerful processor with architectural enhancements, advanced acceleration engines and specialized peripherals. As a result, embedded applications of software- and pin-compatible have become more complex with each new generation. For example, many MCUs now have DSP-type instructions to support high-performance signal processing, USB and Ethernet data rates are magnitudes of order faster. and low-power operation is no longer just an option but rather an essential design factor that must be considered early in the design process.

The only way to stay competitive is to build upon an MCU architecture that is not just flexible but continues to evolve over time by integrating new functionality that increases application performance while

lowering overall system cost. Selecting an MCU that offers only limited performance, memory, and peripheral options will result in a system that needs to be completely redesigned in only a few years. By choosing an MCU with a broad roadmap devices with a mature tool chain and an extensive support ecosystem, developers can be sure that their designs will not only be cost-effective but be able to carry them well into the future.

#### So Many Choices

When an engineer begins looking for a new architecture, there's usually a strong need driving the change. Perhaps there isn't enough performance with the current architecture, even with the highest-end family member, or the memory and peripheral options don't offer the right mix. Once the design is opened for review, it's worth looking beyond just what is

needed at the moment to see what else a new MCU family can offer to improve the value a product provides customers. Introducing an advanced communications peripheral such as USB, for example, may open new markets without negatively impacting system cost. As a consequence, the selection of a new MCU platform directly determines what future products can be designed as well.

For the engineer starting a new design or needing a new architecture with more capacity for an existing design, the extraordinary variety of MCU options can seem overwhelming. ST, for instance, offers more than 250 different devices in its STM32 product line alone. Perhaps surprisingly, selecting the optimal processor for an application is actually easier today than it ever has been.

In the early days of electronics design, developers were

limited to a short list of MCU architectures, each offering a variety of Flash, RAM, I/O, and UART options. Right-sizing an MCU to an application could be a difficult estimation. For example, if the estimation of the amount of Flash required to hold program code was too low, this could force a developer to switch to another processor family late in a product's design cycle and require a redesign that delayed time-to-market and increased cost substantially.

Today's MCU architectures seem to provide an even more difficult challenge to estimate code size and performance. Specialized DSP-specific instructions, for example, both accelerate signal processing tasks and reduce the amount of code required to complete these tasks. Advanced DMA controllers, for example, can significantly impact performance by managing the data flow of an application in

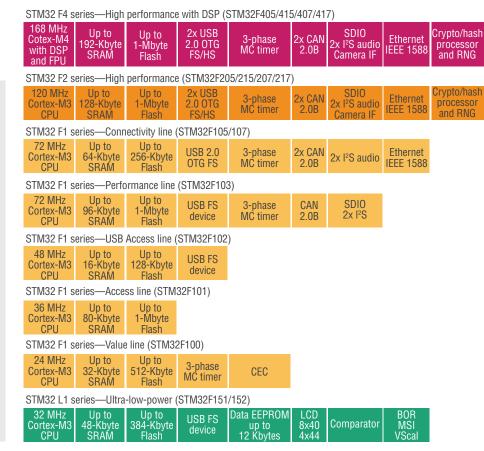

Figure 1 The STM32 family offers more than 250 code-compatible MCUs, giving developers unparalleled flexibility in right-sizing an MCU to their application.

the background. Similarly, a wide range of dedicated accelerators implemented in hardware are available to speed processing of all kinds of data, including cryptographic security, CRC calculations, and communications protocols, to name just a few. The availability of application-specific peripherals also increases performance through intelligent management of peripheral data and functions to further offload the main CPU.

However, the ability to accurately estimate application performance and memory requirements before any code has been written is no longer as critical an exercise as it once was. All 250+ STM32 MCUs are not only code compatible, more importantly the integrated peripherals and system functions are compatible across the entire line. This gives developers unparalleled flexibility in right-sizing an MCU to an application (see Figure 1). If more performance is required. there are numerous choices available further up the product line. Likewise, if an application can be implemented using fewer cycles, another MCU further down the product line can be

used instead without any need to recode the application. From this perspective, the extended variety of options within the STM32 family actually makes it easier to select the ideal MCU for an application.

This variety of options also enables manufacturers to leverage the same architecture and code base across an entire product line. The STM32 F1 Value Line, for example, provides the right mix of peripherals, memory, and performance for low-end applications where price is tantamount. For a high-end version of the same system, the STM32 F4 provides the range of peripherals needed for a full-featured device backed with the processing capacity and memory to support these features. With complete compatibility between devices—code, pin, peripheral, and system functions—manufacturers can reuse their existing code base and hardware designs thereby reducing the development cost of next-generation devices as well as significantly accelerating time-to-market.

#### The ARM Advantage

When evaluating an MCU architecture, it is useful to look at the entire design platform being offered. Recently, EETimes conducted a survey asking engineers what they considered the most important factors in selecting an MCU. The cost of the device was third. Performance ranked second. The most important factor: development tools.

Given the software complexity of today's embedded systems, software development represents a significant portion of the cost of a system. Software also impacts time-to-market more than any other design factor. From this perspective, it is not surprising that development tools are the most important consideration to developers.

The various ARM cores have the broadest support and tools ecosystem compared to any other MCU architecture. Tools are available from many different suppliers, ensuring a good range of tools that are easy to use. With so much competition, these tools have to be superior to survive. In addition, tool suppliers further differentiate themselves by

Given the software complexity of today's embedded systems, software development represents a significant portion of the cost of a system...from this perspective, it is not surprising that development tools are the most important consideration to developers.

offering tools designed for specific market segments. As a result, these tools provide greater functionality than a proprietary MCU supplier can supply on its own.

The ARM Cortex-M has also become the standard MCU architecture in many application markets. Its architecture has been field-proven and is well-established with an extensive tools ecosystem and widespread support from industry players. Designed from the ground up to meet the real-time performance and memory requirements of embedded applications, the Cortex-M core offers:

#### **Integrated Interrupt Controller:**

The Cortex-M architecture integrates the interrupt controller rather than requiring silicon manufacturers to add their own as they have to with the ARM7 and ARM9 cores. This results in faster interrupt handling and more deterministic application response.

# Single Instruction Set: The ARM7 and ARM9 cores tried to address conflicting performance and code density requirements by interworking the architecture's original 32-bit instruction set with the 16-bit Thumb instruction set. This approach required developers

to manually use a special subroutine branch instruction to switch between instruction sets based on whether they needed performance or code density at the moment. It also introduced design complexity and forced developers wanting to work in C to have to involve themselves with lower level implementation details. The Cortex-M architecture automatically blends the benefits

of performance and code density with the Thumb2 instruction set, freeing developers to focus on the application.

Better computational capabilities: The Cortex-M introduces advanced computational capabilities—including a single-cycle 32-bit multiply, hardware divide instructions, DSP functions, and saturated math, to name a few—to support the various

types of complex signal processing and computational analysis many embedded applications require today.

RTOS: The Cortex-M architecture has been designed to support real-time operating systems. For example, privilege modes enable kernel-level schedulers to guarantee real-time responsiveness.

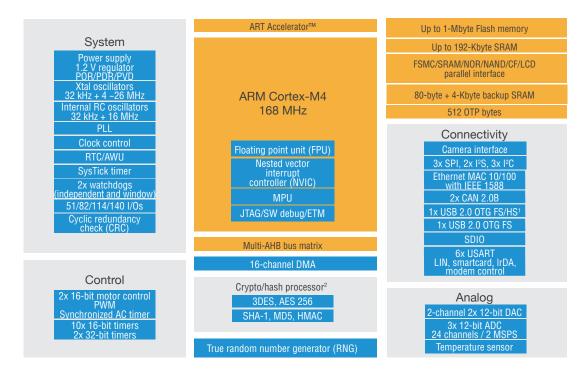

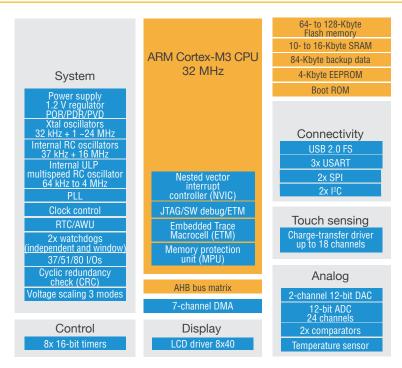

Figure 2 ST has expanded its STM32 MCUs beyond the base Cortex-M architecture with a variety of integrated peripherals to create a wide range of MCUs that optimize performance, memory, and cost for nearly every embedded application.

#### The STM32 Architecture

The ARM Cortex-M architecture provides an excellent foundation for embedded design. However, performance and reliability are not determined by the CPU architecture alone. For this reason, ST has expanded its STM32 MCUs beyond the base Cortex-M architecture with a variety of integrated peripherals to create a wide range of devices that optimize performance, memory, and cost for nearly every embedded application (see Figure 2). Combined together, these peripherals provide significant benefits to manufacturers:

Reduced BOM: Some of the STM32's integrated peripherals are core components that embedded systems require, such as a real-time clock, internal oscillators, and supervisor functions. While individually these components are relatively inexpensive when implemented externally, their combined integration within the MCU results in a substantially lower bill of materials (BOM), smaller form factor, and simplified board layout.

Increased Performance: Multiple DMAs, integrated connectivity for USB OTG and Ethernet, and application-specific peripherals

like hardware-based encryption all offload CPU processing to increase overall system efficiency.

#### **Complete Compatibility:**

Developers can easily migrate designs between different STM32 MCUs as all STM32 MCUs are code-compatible. Most STM32 devices are also pin-compatible, simplifying hardware redesign as well. Furthermore, STM32 MCUs are also peripheral and system function compatible, meaning that even migrating low-level code is a seamless and transparent process.

Unparalleled Accuracy: By integrating the analog signal chain – including high-precision 12-bit ADCs and advanced cascadable control timers that run at full core speed – precise sampling, control, and timing functions are possible.

Enhanced Safety: Peripherals such a windowed watchdog and automatic clock switchover circuit are essential for the design of products that must meet high-reliability standards, including consumer electronics, white goods, and industrial applications.

Flexible Voltage: STM32 MCUs support a range of supply voltages, as wide as 1.65 to 3.6 V for some devices. This allows the system to operate from a single battery without an external regulator. In addition, most GPIOs are 5 V tolerate for compatibility with industry standards. (For a detailed exploration of how the high-level of integration of the STM32 architecture simplifies application

# Optimized for Your Application

design, see page 27.)

ST was the first major semiconductor company to bring the Cortex-M architecture to market and has the largest portfolio of devices available from any company with core speeds from 24 to 168 MHz and memory options ranging from 16 KB to 1 MB of Flash. ST has developed four separate series within the STM32 family that focus on different applications

#### 4 product series

Common core peripherals and architecture:

Communication peripherals: USART, SPI, I2C Multiple general-purpose timers Integrated reset and brown-out warning Multiple DMA 2x watchdogs Real-time clock Integrated regulator PLL and clock circuit External memory interface (FSMC) Dual 12-bit DAC Up to 3x 12-bit ADC (up to 0.41 μs) Main oscillator and 32 kHz oscillator Low-speed and high-speed internal RC oscillators -40 to +85°C and up to 105°C operating temperature range Low voltage 2.0 to 3.6 V or 1.65/1.7 to 3.6 V (depending on series) 5.0 V tolerant I/Os Temperature sensor

Figure 3 The STM32 family is comprised of four separate series of MCUs focusing on different applications with core speeds from 24 to 168 MHz and Flash memory options ranging from 16 KB to 1 MB to provide the ideal mix of performance and peripherals at the lowest cost.

to provide the ideal mix of performance and peripherals at the lowest cost (see Figure 3):

**High Performance:** The entire architecture of the STM32 F4 and STM32 F2 MCU series has been tuned to provide high-performance without compromising flexibility (see sidebar, Introducing the STM32 F4). Built upon a 90 nm process, ST's innovative Advanced Real-Time (ART) memory accelerator technology, and a zero-wait execution path, STM32 F4 and STM32 F2 series MCUs provide outstanding performance (up to 168 MHz/210 DMIPs for the STM32 F4) and power efficiency (only 22.5 mA at 120 MHz for the STM32 F2). Its multilayer bus matrix enables the highest

levels of multiprocessing by supporting simultaneous transfers to multiple peripherals and memory while the CPU continues to execute code. In addition, its Flash memory has been designed to remove access bottlenecks typical of other MCUs. This enables the CPU to operate at its full speed when executing from Flash. (For more information on developing real-time, high-performance applications, see page 12.)

#### **General-Purpose Applications:**

ST offers three general-purpose MCU series based on the STM32 F-1 architecture with varying performance, memory, and peripheral capabilities. For simple applications, Access Line MCUs provide

36 MHz performance with the STM32 architecture's extensive selection of advanced peripherals. For applications needing to support USB, USB Access Line MCUs operate at 48 MHz and have an integrated USB port. For higher end devices, Performance Line MCUs offer 72 MHz performance, USB, and application-specific peripherals like ST's unique 3-phase Motor Control Timer.

Superior Connectivity: The STM32 Connectivity Line makes networking economical by integrating an embedded Ethernet MAC with its own dedicated DMA and IEEE 1588 precision time protocol hardware support. Turnkey consumer

device connectivity with full USB functionality is enabled through the USB 2.0 OTG (On-The-Go) peripheral, and dual CAN interfaces make this the MCU of choice for CAN gateways. The STM32 Connectivity Line also offers two audio-class I2S interfaces to meet the needs of most consumer audio applications. (To see how to design systems with more efficient connectivity, see page 35.)

Cost-Sensitive Design: STM32 Value Line microcontrollers provide the least expensive path to market. Ideal for cost-sensitive consumer, appliance, and industrial applications, STM32 Value Line MCUs offer the performance of a 32-bit

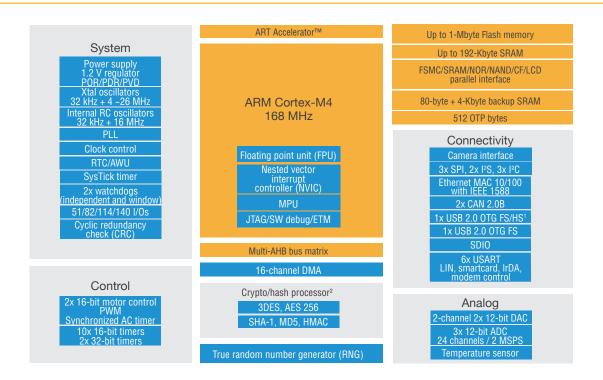

#### Introducing the STM32 F4

As the world's highest performance Cortex-M microcontroller, the STM32 F4 is ST's flagship MCU operating at 168 MHz and providing 210 DMIPS. Based on the ARM Cortex-M4 core, it provides advanced floating point and digital signal processing capabilities to enable compute-intensive processing across a broad range of applications ranging from point of sale, industrial automation, solar, transportation, medical, security, consumer, communications, and test and measurement. The ultra-low power STM32 F4 is built on ST's 90 nm process which allows

the CPU core to run at only 1.2 V. In addition, with dynamic voltage scaling capabilities and ST's innovative Adaptive Real-Time (ART) memory accelerator which maximizes processing performance equivalent to 0-wait state execution, the STM32 F4 offers outstanding power efficiency of just 230  $\mu\text{A/MHz}$  or 38.6mA at 168 MHz executing Coremark benchmark from Flash memory. The STM32 F4 also integrates a wide range of application-specific peripherals and interfaces, providing advanced processing capabilities and turnkey communications with a single chip.

#### 4 starter kits, numerous boards

#### STM32 promotion kits

STM32VL DISCOVERY

#### 13 different RTOS and stack solution providers

# SYSTEMS DEVELOPMENT TOOLS DIGITAL Green Hills: SYSTEMS DEVELOPMENT TOOLS DIGITAL GREEN HILLS: SOFTWARE, INC. RAISONANCE Quadros Enterruche Streen Conferent Local Conference Conference

#### More than 15 different development IDE solutions

Figure 4 Development tools for the STM32 come from the world's largest vendor ecosystem, providing the evaluation boards, compilers, and development software designers need to accelerate their development.

core at 16-bit pricing, giving developers the headroom to implement enhanced features and provide superior products compared to the competition. These MCUs also have a 3-Phase Motor Control Timer to improve performance for motor control applications, flexible static memory controller, LCD parallel interface, and a CEC (Consumer Electronics Control) interface for communicating

with other devices over HDMI. Running at up to 24 MHz, STM32 Value Line MCUs offer an excellent balance of cost, performance, and peripherals, making it the ideal choice for developing cost-effective applications traditionally addressed by 16-bit MCUs.

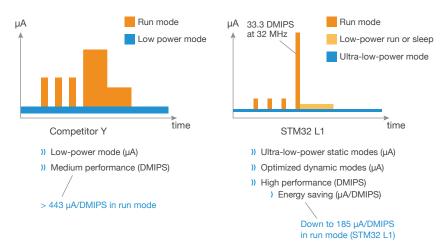

**Ultra-Low Power and Portable Devices:** The feature-rich

STM32 L1, based on ST's

industry-leading EnergyLite™

technology implemented in ST's 130 nm ultra-low leakage process technology, is the industry's only MCU offering ultra-low power (down to 185 µA/DMIPS) with high performance (up to 33 DMIPS) for maximum energy efficiency. Multiple innovative low power operating modes enable developers to further minimize power consumption depending upon the current

operating requirements. For example, a typical low-power MCU can conserve power by dropping the clock frequency; however, the core still runs at its full supply voltage. The STM32 L1's integrated regulator gives developers the option to also reduce the core operating voltage as the operating frequency drops, enabling even higher power efficiency. Stop Mode with

#### Everything you need to discover STM32 F4 32-bit ARM Cortex<sup>™</sup>-M4 based MCUs featuring:

- )) Evaluation board

- )) Embedded ST-LINK/V2

- )) USB interface for debugging and programming

- )) Numerous examples available on www.st.com

Figure 5 ST's STM32 Discovery kits provide everything developers need for a quick start to a production design with minimal tools investment.

RTC and full RAM retention requires only 1.3 µA, and lowpower run mode clocked at 32 kHz provides access to the full capabilities of the CPU while bringing power consumption down to 10.4 µA. Supporting a wide supply voltage range from 1.65 to 3.6 V, flexible 1.8 to 3.6 V operation for all digital and analog functions, optional LCD controller, integrated AES, and a variety of enhanced security and safety features, the STM32 L1 is ideal for a wide range of applications, including portable medical, alarm systems, factory automation, mobile devices, metering, and sensors.

(To learn more about achieving ultralow power consumption, see page 20.)

#### **Unparalleled Flexibility**

Software- and pin-compatibility between the various STM32 series makes for a broad range of devices that allow developers to easily step up or step down performance across a product line. Developers have the ability to develop first prototypes using a high-performance STM32 with large memory to speed development. Once the application code is in place, the MCU can be scaled down to a slower device with less memory that also eliminates peripherals which aren't needed to cost reduce the system.

(To learn more about extending a product line by scaling the MCU and reusing IP, see page 42.)

ST also offers MicroXplorer, a graphical tool which simplifies pinout configuration of STM32 MCUs. Since the same pin can be used for different peripherals and functions (GPIO, USART Tx. ADC input channel, etc.). MicroXplorer assists developers by defining a pinout that maps the pins needed for a peripheral based on the current operating mode. This not only speeds initial MCU configuration but supports reconfiguration of a system based on new application requirements.

Development tools for the STM32 come from the world's largest vendor ecosystem. offering the evaluation boards. compilers, and development software designers need to accelerate their development (see Figure 4). In addition, everything needed for a quick start to a production design with minimal tools investment is available in ST's Discovery Kits for the STM32 F2/ F4, STM32 Value Line, and STM32 L1. Providing the ideal development environment for rapidly evaluating, learning, and prototyping, each kit comes with an in-circuit ST-LINK debugger/ programmer for non-intrusive debugging, full development

tool chain, ready-to-run example applications, and schematics for reference designs (see Figure 5). Kits also have an extension connector providing access to all of the STM32 pins and can be used to debug prototype boards as well.

To keep up with changing application requirements, developers need a flexible MCU architecture that offers flexible performance. The breadth of the STM32 family allows developers to select devices with the highest performance, the lowest power, the best price, and the right mix of peripherals. Because STM32 MCUs are software- and pin-compatible, developers can use the same tool chain and libraries to accelerate and simplify design across an entire product line. And with the broadest ARM Cortex-M family on the market. the STM32 architecture offers an ever-expanding line of MCUs that meet the evolving needs of developers both today and tomorrow.

# Maximizing Performance for Real-Time Embedded Systems

By Reinhard Keil, Director of MCU Tools, ARM Germany GmbH Ian Johnson, Product and Third Party Relations Manager, ARM Ltd Shawn Prestridge, Sr. Field Applications Engineer, IAR Systems Alec Bath, Applications Engineer, STMicroelectronics

Many embedded applications—including control systems, digital audio/video devices, industrial automation, portable medical instruments, and diagnostic test equipment—require deterministic system behavior to meet realtime deadlines and process data within a meaningful time frame. With increased interest in greater operating efficiency, network capabilities, and higher performance, these systems also require more advanced signal processing capabilities.

In the past, embedded applications that require real-time control and signal processing capabilities have had to compromise by either using an MCU or DSP but not being able to use both. Using a separate MCU and DSP will introduce complex multiprocessor issues into the design flow as well as the need to

handwrite assembly code for critical-loop algorithms.

Rather than complicate or compromise design, ST's STM32 F4 MCU architecture intelligently blends the capabilities of an MCU with a DSP to provide a powerful yet easy to program platform. Based on the ARM Cortex-M4 core, the STM32 F4 is supported by an extensive ecosystem that enables systems to deliver high performance and advanced signal processing using the CMSIS DSP Library.

#### The STM32 F4: The Industry's Highest Performance Cortex-M-based MCU

Maximizing performance is an art. And given that the majority of an embedded application's functionality is implemented in software, the efficiency of a system will depend primarily

upon how well it is coded. The STM32 architecture offers a powerful platform with hardware-based accelerators and application-specific peripherals that simplify application design while offloading processing and memory management from the CPU.

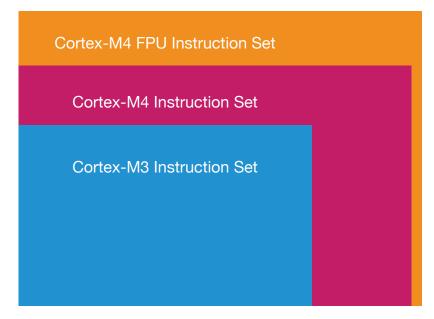

The STM32 architecture is built upon the ARM Cortex-M3 and Cortex-M4 cores using a Harvard architecture with separate instruction and data buses for

parallel instruction fetching and data loads and stores. All STM32 MCUs are programmed using the rich, unified Thumb-2 instruction set that provides 32-bit performance while supporting 16-bit Thumb instructions for the smallest code density and memory requirements; up to ten lines of code can be replaced with a single 32-bit instruction (see Table 1). In addition, 16- and 32-bit instructions can be used without having to switch modes.

| Feature                      | Cortex-M3 cycles | Cortex-M4 cycles |

|------------------------------|------------------|------------------|

| High-precision MAC           | 3–7              | 1                |

| DSP instructions             | 1–2              | 1                |

| Saturated arithmetic         | 1                | 1                |

| Bitwise operations           | 1                | 1                |

| Mixed bit-width capabilities | Not available    | 1                |

| Packed data processing       | Not available    | 1                |

| SIMD capabilities            | Not available    | 1                |

Table 1 Cycle execution times for advanced instructions

For deterministic, low-latency responsiveness, a Nested Vectored Interrupt Controller (NVIC) provides a worst-case interrupt response time of 12 cycles. This includes automatic saving of corruptible registers as well as handling of exception prioritization and nesting. In addition, if another interrupt occurs before the current one has completed, the MCU recognizes this and can respond to the next interrupt within just 6 cycles. Called tail-chaining, this approach to interrupts increases performance and responsiveness for interruptdriven applications. This enables the system to be maintained in a low-power state, to rapidly wake to service an interrupt, and then re-enter sleep state on exit from the interrupt handler.

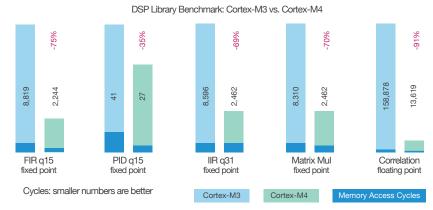

With ST's flagship MCU—the STM32 F4—developers can give designs based on the STM32 F2 a substantial increase in performance without having to rewrite their application. At a raw performance level, fixed-point DSP functions execute on the Cortex-M4 core-based STM32 F4 up to twice as fast as they do on a Cortex-M3 core-based STM32 F2 while floating-point functions execute

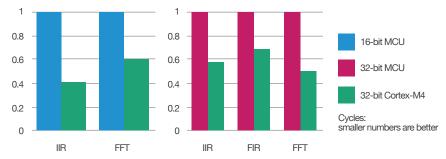

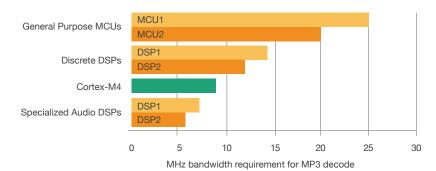

up to 10X faster (see Figure 1). Compared to the leading 16- and 32-bit MCUs with DSP extensions, the Cortex-M4 core is twice as efficient when performing the fundamental operations—FIR, IIR, and FFT—that make up a significant portion of communications. audio, and motor control processing (see Figure 2). This means that low-cost consumer devices can perform real-time digital content processing like MP3 while leaving sufficient bandwidth for other application tasks (see Figure 3).

Even though the STM32 F4 is based on the Cortex-M4 core, STM32 F4 MCUs support all of the features of STM32 F2 MCUs, making it straightforward to migrate designs which need more performance. The tremendous performance gains of the STM32 F4 come from its higher clock rate and several powerful new capabilities:

Single-cycle MAC: The ability to perform a multiply-and-accumulate (MAC) in a single cycle provides substantial performance improvements for critical-loop algorithms.

**DSP extensions:** With SIMD instructions (single instruction,

Figure 1 Fixed-point DSP functions execute on the STM32 F4's Cortex-M4 core up to twice as fast as they do on an STM32 F2's Cortex-M3 core while floating-point functions execute up to 10X faster.

Figure 2 Compared to the leading 16- and 32-bit MCUs with DSP extensions, the STM32 F4's Cortex-M4 core is twice as efficient when performing the fundamental operations—FIR, IIR, and FFT—that make up a significant portion of communications, audio, and motor control processing.

Figure 3 The STM32 F4 is able to perform real-time digital content processing like MP3 decoding while leaving sufficient bandwidth for other application tasks.

multiple data operations per cycle), saturating arithmetic capabilities, and a packed data format to increase processing efficiency, the STM32 F4 is capable of accelerating performance in a wide range of applications.

FPU: The Floating Point Unit is a single-precision engine available on all STM32 F4 MCUs to provide hardware-assisted addition, subtraction, multiplication, division, fused MAC, and square root. The FPU can be individually powered down when it is not in use.

Larger SRAM: With a large 192 KBytes of SRAM, developers have more memory available for optimizing application performance.

#### The STM32 Advantage

The STM32 architecture builds upon the foundation of the ARM Cortex-M3 and Cortex-M4 cores. However, ST has integrated numerous innovative technologies to enable the STM32 architecture to achieve the highest performance of any Cortex-M processor-based MCU in the industry with ultra-low power consumption:

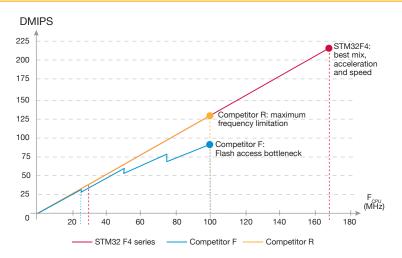

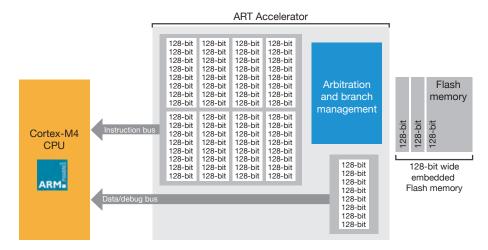

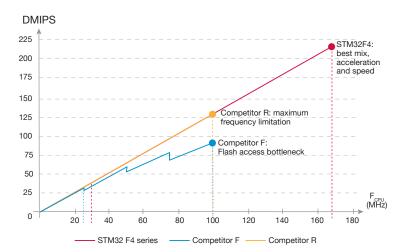

**ART Accelerator:** ST's Adaptive Real-Time (ART) memory accelerator technology is a key performance differentiator for STM32 F2 and STM32 F4 MCUs when executing from Flash. At high CPU speeds. Flash access can become a bottleneck and significantly reduce performance by introducing undesirable wait states. The ART Accelerator uses a prefetch queue and branch queue to store first instructions and constants associated with branches in code. With its deep caches, 128-bit wide memory interface, and background operation, wait states can be effectively eliminated when executing from Flash. Rather than have performance degrade as clock speed increases, STM32 F2 and STM32 F4 MCUs are able to consistently provide their full performance across all clock speeds (see Figure 4).

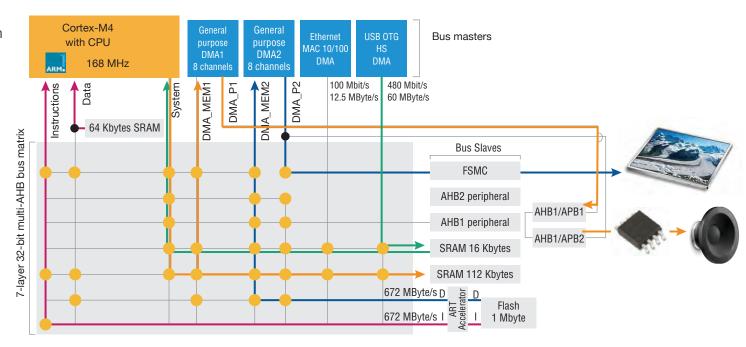

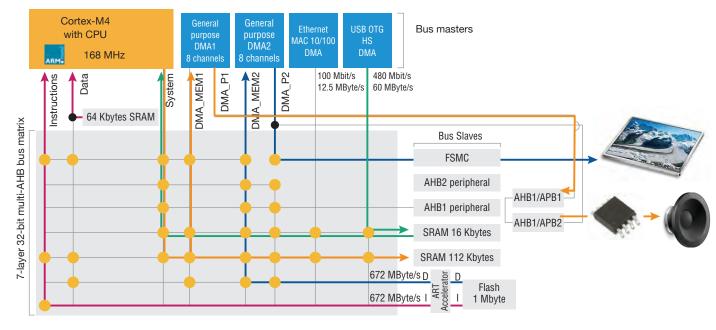

#### **Multi-layer Bus Interconnect:**

With the great number of peripherals in the STM32 architecture, performance is highly dependent upon the efficiency with which the MCU can move data internally between the CPU, peripherals, and memory. The 7-layer bus

Figure 4 ST's Adaptive Real-Time (ART) accelerator technology utilize a deep branch cache, 128-bit wide memory interface, and background operation to effectively eliminate wait states when executing from Flash, enabling STM32 F2 and STM32 F4 MCUs to consistently provide their full performance across all clock speeds.

matrix that interconnects

STM32 MCUs (see Figure

5) enables simultaneous

transfers between multiple

masters and slaves without

requiring CPU involvement.

This provides STM32 MCUs

with a tremendous interconnect

capacity that eliminates

peripheral and memory access

bottlenecks for the highest

operating performance.

#### **Dedicated DMA engines:**

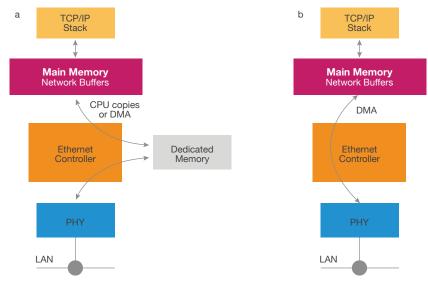

Embedded systems must be able to support multiple realtime data streams, including one or more communications links, high-frequency data from multiple ADC channels, and accesses to different memory blocks. To facilitate the greatest throughput, the STM32 F4 integrates multiple DMA engines, including dedicated DMA engines for its Ethernet and USB interfaces to support true zero-copy functionality. This enables the system to support various data streams with no contention between high-speed interfaces and without loading the CPU.

Application-Specific

Accelerators: The STM32

architecture offers a variety of

hardware-based engines to

accelerate processing for various

applications. For example,

efficient security can be easily added to communications using the integrated cryptographic/hash engine available on many STM32 MCUs. Packets are sent to the engine for processing and a flag is set or interrupt triggered when the result is available. Likewise, the hardware-based CRC engine offloads communications overhead from the CPU.

Together, these enhancements— ART Accelerator, multi-laver bus interconnect, dedicated DMAs, and applicationspecific accelerators—make for an architecture that is highly optimized for real-time embedded processing. In addition, the ability to support simultaneous memory and peripheral transactions enables a single STM32 F4 MCU to maintain several high-speed interfaces, perform computeintensive signal processing, and manage a GUI-based display with advanced HMI functions.

# Accelerated Development and Optimized Performance

To make the complexity of the STM32 architecture transparent during development, ST and its partners, including IAR and Keil,

Figure 5 The 7-layer matrix that interconnects STM32 MCUs with peripherals and memory enables simultaneous transfer between multiple masters and slaves without requiring involvement from the CPU. This provides STM32 MCUs with a tremendous interconnect capacity that eliminates peripheral and memory access bottlenecks for the highest operating performance.

The ability to support simultaneous memory and peripheral transactions enables a single STM32 F4 MCU to maintain several high-speed interfaces, perform compute intensive signal processing, and manage a GUI-based display with advanced HMI functions.

offer a great variety of innovative tools that go beyond the standard compiler and debugger so that developers can maximize performance without having to create low-level code which cannot easily be ported when the describing how to use them most efficiently under different operating conditions. In addition, if major specification changes are subsequently made to the system, so long as developers work within the framework, it

The multitasking capabilities of an RTOS also eliminate the need for polling interfaces or holding up the CPU while waiting for a critical task to complete.

design needs to move to a lower cost or higher performance MCU. These tools not only accelerate time-to-market by simplifying design, they make it easier to focus on optimized performance.

To accelerate development, ST provides a configuration wizard for creating a base framework upon which developers can quickly build applications. Configuration of peripherals is non-trivial and failing to take full advantage of each of the MCU's application-specific peripherals can negatively impact performance. The framework provides optimized drivers for all of the STM32 peripherals with documentation

will be flexible enough to allow developers to quickly adapt to the new requirements.

Real-time operating systems (RTOS) like RTX from Keil™ provide a reliable framework that efficiently manages realtime processes and allows applications to fully utilize the STM32 architecture. Task management can quickly become extremely complex, and choosing an embedded RTOS that has been specifically designed to exploit the integrated capabilities of the STM32 simplifies the process of managing multiple real-time tasks while optimizing allocation of processor resources to

ensure real-time deadlines are met. For example, interrupts never need to be turned off for the RTOS. The multitasking capabilities of an RTOS also eliminate the need for polling interfaces or holding up the CPU while waiting for a critical task to complete. Instead, available CPU cycles can be allocated to other tasks until an interrupt signals the completion of the task.

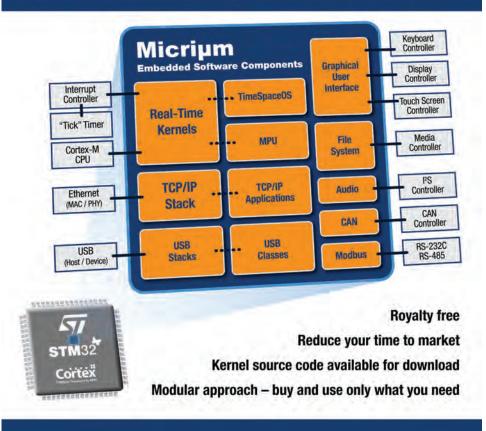

Developers can also rely upon the extensive ARM development ecosystem to speed design with off-the-shelf code which has been specifically adapted for the STM32 architecture and optimized for performance. Networking applications, for example, can make use of middleware supplied by ARM and other companies for quickly creating efficient Flash file systems, TCP/IP stacks, and CAN controllers, among other capabilities. Application-specific software is available as well: ST and its partners, for example, offer a variety of solutions for consumer audio. ST's audio library is designed to ensure that audio processing is completed in time so that users will not hear any pops or clicks.

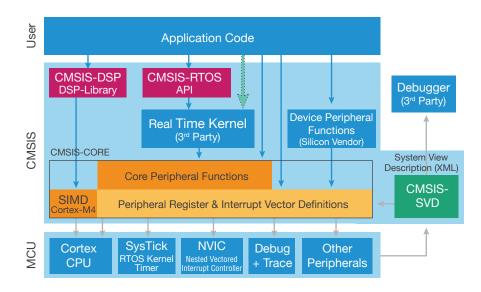

Middleware and libraries are easy to integrate into STM32based systems because of the Cortex Microcontroller Software Interface Standard (CMSIS) which provides a rich collection of building blocks for accelerating embedded system design. The CMSIS CORE library offers a standardized interface for all Cortex-M-based MCUs while the SVD library provides a System View Description for peripherals to speed design and facilitate code compatibility among processors. The RTOS library comprises a standard API for RTOSes to enable interoperability with an extensive variety of software templates, middleware, and libraries.

For applications requiring efficient signal processing capabilities, the CMSIS DSP library offers more than 80 algorithms including vector operations, matrix computing, complex arithmetic, filtering, and PID and Fourier transforms. Designed to make DSP programming easy for developers used to working with MCUs, the CMSIS DSP library enables engineers to quickly develop a wide range of complex and reconfigurable systems across industrial,

#### Working With Your Compiler

By Shawn Prestridge, Senior Field Applications Engineer, IAR Systems

Today's compilers can generate application code from C source code that provides nearly the same or better efficiency than hand-coded assembly. However, since code can be optimized in terms of performance, size, and/or power, compilers need to be guided to achieve the optimal balance for a given application. Compilers do their best to optimize code, but ultimately programmers who assist the compiler by writing "compiler-friendly" code will achieve higher efficiency and better performance.

- )) Be careful not to start the optimization process before the functionality of code has been verified. Optimized code can look bizarre, making it difficult to debug. In addition, it will be much easier to determine whether a problem is the result of a bug or an unintended consequence from some element being optimized out of the system.

- Nonly call a function once. Compilers cannot predict the side effects of functions at compile time. Therefore, if an identical call is made twice, the compiler cannot assume they will have the same result and will have to make the call twice as well. Calling the function once and putting the result in a variable allows the compiler to store the result in an easily accessed register.

- )) Pass by reference rather than copy. Passing by reference saves significant code space, memory, and execution cycles by avoiding copying data during a function call, especially if large arrays are involved. However, passing by copying may be necessary if the function must be prevented from having direct access to data.

- Inline functions. Inlining generates function code rather than a function call. This eliminates the overhead of a function call to improve performance but can increase code size. IAR's Embedded Workbench, for example, makes intelligent decisions for when to inline code to balance performance and code size to ease this optimization technique. In addition, developers always the option to override these decisions.

- We appropriate data sizes. The STM32 is a 32-bit architecture. Using a different data size can force the compiler to shift, mask, and sign-extend operations, leading to lower performance and issues that arise from signedness and casting.

- )) Use signedness with care. Using signedness when it is not required can increase code size (i.e., certain operations may require an extra

automotive, medical, and military applications. Available free of charge, the CMSIS DSP library is provided as C source code so the compiler can optimize the code to the application (i.e., performance versus code and data size). Code is portable across all Cortex-M-based MCUs. enabling simple migration of DSP functionality across the STM32 families. In addition, the CMSIS DSP library has been optimized to take advantage of the optional floating point unit (FPU) integrated into the Cortex-M4 architecture.

# Debugging to Optimize Performance

To optimize a system, developers need run-time visibility into operations to verify how various subsystems interact with each other and to identify, locate, and resolve errors quickly. However, many embedded systems, including systems maintaining a communications link or providing control data, cannot be stopped and then restarted. Developers, however, need more than just a "snapshot" of the moment when code is halted so they can analyze system

behavior and identify real-time performance bottlenecks.

STM32 MCUs have superior debugging capabilities integrated into the MCU, including hardware breakpoints, onthe-fly read/write access to variables and memory contents, and instruction stream tracing for advanced code execution analysis, all without having to go through the processor or halt its execution. Rather than requiring code to be instrumented (and thereby impacting code execution), developers can use the integrated Embedded Trace Macrocell (ETM) or serial wire tracing to non-intrusively access the system, including capabilities such as monitoring the RTOS or tracking the different threshold levels of an ADC.

Companies like IAR Systems and Keil offer an array of tools which utilize the trace technology implemented within the STM32 MCUs to assist developers in maximizing application performance and reliability by giving them complete visibility into program execution and MCU operations. For example, embedded trace data can be streamed to a PC hard drive to collect long-term run-time

- test-and-jump condition to handle negative numbers) or have intended consequences (i.e., shifting or masking data that has been sign-extended).

- )) Avoid explicit casting. Casting is not a free operation. Casting to a larger type can introduce unnecessary sign-extended overhead, invoke the floating point library, or corrupt a pointer (i.e., if developers use ints and pointers interchangeably).

- Invoke libraries intentionally. Using print() where you can use printf() may cause a larger library to be included in your application, needlessly consuming code space for functions that are never called.

- )) Baseline your code. A dramatic increase in code size from simple changes may mean a previously-unused library has been invoked through an unintentional cast.

- Novid using global variables. A function that accesses a global variable multiple times will have to repeatedly read that value from memory. Rather, read the global variable into a temporary variable that is local to the function and the compiler may be able to hold it in a register for better performance.

- )) Group function calls. When function calls are separated by other operations, each call forces the compiler to store any registerallocated variable to memory. When calls are consecutive, these values only need to be saved once.

- Navoid inlining assembly. Since the compiler knows nothing about inlined assembly, it cannot optimize the code around it. Putting assembly code in a separate file frees the compiler to optimize the rest of the code.

- Don't write "clever" code. Writing an expression in the fewest lines of C code with conditional values often results in difficult-to-read code that can actually require more instructions and take longer to execute because of the need to store temporary values or perform a function multiple times.

- Maccess structures in order. Rather than bouncing through a structure and requiring complex pointer manipulation, accessing elements in order enables the compiler to use a fast increment instead.

Powerful search and filtering capabilities enable developers to focus their optimization efforts where they will yield the most gains. data for offline analysis. Having the entire execution history of an application synchronized to C source code complete with timing information is especially useful for analyzing a wide range of issues, including sporadic problems that arise from data that impacts throughput and increases the load on the CPU. Another benefit of using performance analysis is that it shows developers the actual impact certain coding techniques have on performance. Many times code can be written

including how many times an exception has been entered and the min/max time spent in each exception. Display of event counters can be used to reveal system behavior such as when extra cycles are taken to execute instructions due to

intrusive instruction stream so that testing is done on final, optimized code running at full speed. Data is color-coded and summarized by function or module and can be saved for documentation. To view a video showing how to perform code coverage, click here.

The STM32's ETM provides a complete, non-intrusive instruction stream so that testing is done on final, optimized code running at full speed.

corruption or incorrect timing. Powerful search and filtering capabilities combined with different reporting and graphing options enable developers first to quickly sort trace data to determine which areas of code the application spends most of its time executing and then focus their optimization efforts where they will yield the most gains.

Performance can be analyzed from a timing perspective for an entire module or as narrow as a single line of code to expose spikes in performance that might otherwise pass unnoticed. For example, a change in task priority may create a conflict with a communications link, resulting in lost data and the need to request a retransmission

different ways, such as a function outputing a single character or a whole line. Often, one of these approaches will yield better performance. Over time, developers will learn which approaches are more efficient so they can change how they program and write optimized code from the very start.

A system can also be analyzed based on changes to variables. Signals/variables can be monitored graphically with accurate timing information showing change across time as well as any instructions that have modified a variable. The STM32 debugging capabilities can also be extended to capture detailed statistical information about exceptions and interrupts,

memory contention, overhead from handling exceptions, cycles spent in sleep mode, cycles spent accessing memory, and number of folded branch instructions.

For mission-critical applications, software validation requires code coverage. Code coverage tracks which lines of code in a program are executed so OEMs can verify that all parts of a system are operational and reliable. Traditionally, this process has been tedious, requiring developers to set a trigger and capture trace data until the internal buffer is full. then reconfigure and run the system again until coverage has been completed. The STM32's ETM provides a complete, non-

With devices ranging from the ultra-low power EnergyLite™ STM32 L1 to the industry's highest performance Cortex-M processor-based MCU, the STM32 F4, developers can find the ideal MCU to meet the processing, power, and cost requirements of nearly every embedded application. The combination of the powerful Cortex-M3 and Cortex-M4 cores with ST's innovative ART Accelerator, multi-layer bus interconnect, dedicated DMAs, and application-specific peripherals provides developers with an unbeatable platform for high-performance applications. In addition, STM32 MCUs are supported by a wide range of advanced tools that speed design, development, and debugging of even the most complex applications.

# Designing for Low Power Applications

By Wolfgang Schmitt, Director Sales North America, Hitex Shawn Prestridge, Senior Field Applications Engineer, IAR Systems® John Knab, Applications Engineer, STMicroelectronics

The increasing complexity of portable and mobile electronics has made power efficiency a primary design constraint which developers need to consider from the very beginning of the design process. In the past, power efficiency was a factor only hardware developers were able to influence using tools like a multimeter and oscilloscope. So much of a system's functionality is now implemented in software, however, that how an application is architected will have a substantial impact on its power efficiency.

ST's STM32 L1 EnergyLite™ architecture provides many features that allow developers to optimize applications for power consumption. In addition to a wide array of advanced peripherals which accelerate performance and offload the main CPU so that devices can spend more time in sleep mode, the STM32 L1 platform offers low-power operation, dynamic

voltage scaling, intelligent peripheral management, and partial sleep modes. STM32 L1 MCUs are built upon ST's 130 nm ultra-low-leakage process technology and provide outstanding power efficiency for a wide range of applications.

With these integrated technologies, developers can maximize utilization of MCU resources while minimizing power consumption so that energy efficiency for all applications can be significantly improved. In addition, by taking advantage of power debugging techniques that correlate power consumption to application code, developers can gain visibility into how their design decisions impact overall power efficiency. Armed with this information, developers can make more informed decisions about how to configure MCU resources and structure application code.

#### Power Modes: More Than Just Sleep

Estimating power used to be a relatively straightforward calculation. Devices were either on or off, and developers could instrument code to measure active and sleep times for an application (i.e. Total Power = Active Current \* Active Time +

background tasks are active and whether a user is currently interacting with the device, the system will switch among several different operating modes potentially thousands of times per second. There are multiple factors that affect dynamic power which can be modified to improve efficiency, including supply voltage,

By taking advantage of power debugging techniques that correlate power consumption to application code, developers can gain visibility into how their design decisions impact overall power efficiency.

Sleep Current \* Sleep Time). With the availability of multiple power modes, however, estimating actual power consumption has become more difficult. Depending upon what

operating frequency, peripheral clock gating, and running from RAM. How fast the system can wake up also affects dynamic power since no instructions are executed while the CPU wakes.

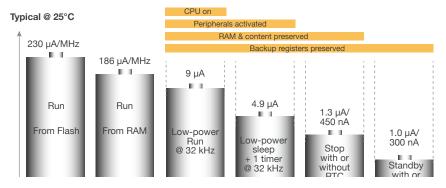

#### STM32 L1 Consumption Values (64 to 128 Kbyte)

**Figure 1** The STM32 architecture enables efficient power management by providing developers with several operating modes. The figures listed here are typical power consumption at 25° C for an STM32 L1 MCU.

Figure 2 The STM32 L1 offers superior power consumption of down to 185  $\mu$ A/DMIPS for those applications which need ultra-low power consumption.

The optimal power strategy for an application depends a great deal upon how the system is aoina to be used. A system that stays on continuously, for example, needs to be architected quite differently compared to a system that spends most of its time asleep. Similarly, a system that must frequently wake the CPU to perform background tasks, such as servicing a communications interface, will need to offer fast responsiveness as well as power efficiency. Power can also be managed by turning off peripherals that are not in use. Each of these considerations results in a distinctly different power profile, and balancing performance, system responsiveness, and power requires that developers select the most efficient operating modes.

The STM32 architecture offers many options for optimizing ultra-low power consumption, including several operating modes (see Figure 1):

Run from Flash: When executing code from Flash, the STM32 L1 offers an outstanding combination of performance and low power with power consumption down to 230 µA/MHz.

Run from RAM: Powering down the Flash and executing code from RAM further lowers power consumption down to 186 μA/ MHz. An additional benefit is that code can be executed at full speed from the internal RAM.

Low-Power Run: In this mode, the CPU is active but operating at 32 kHz. Power consumption drops to 9  $\mu$ A while still enabling the system to be completely available, including all MCU peripherals. This mode is useful for systems that must always be on to monitor system operations but do not always require high performance processing capabilities (see Figure 2). In addition, this mode provides excellent time-to-wake-up.

Low-Power Sleep: This mode puts the CPU to sleep but still keeps some peripherals active for both receiving incoming data and waking the system quickly. Operating at 32 kHz with one timer available, this mode consumes only 4.9 µA and provides a power-effective way to intelligently monitor and wake the system without having to be continuously active.

**Stop Mode:** The CPU and peripherals are shut down in Stop mode. The system can run

**Figure 3** The STM32 L1 (and the STM32 architecture in general) offers a variety of features specifically designed to further decrease power consumption.

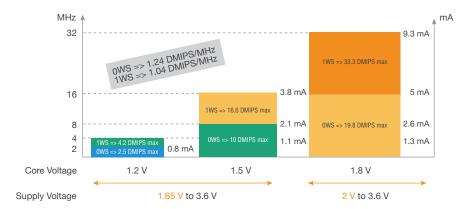

Figure 4 The STM32 architecture supports three core voltage levels—1.8, 1.5, and 1.2 V— to dynamically scale down performance and power consumption when the full processing capabilities of the CPU are not needed. The dynamic voltage scaling figures shown are based on an STM32 L1 in run mode.

at 450 nA without the real-time clock or 1.3  $\mu$ A with the real-time clock active. This mode allows the system to wake more quickly than standby mode.

Standby Mode: This mode provides the lowest power operating mode: only 1.0 µA without the real-time clock or 300 nA with the real-time clock active.

In addition to its numerous operating modes, the STM32 architecture offers several other options for further decreasing power consumption (see Figure 3):

- )) Dynamic Voltage Scaling: The STM32 L1 supports three core voltage levels – 1.8, 1.5, and 1.2 V - to scale down power consumption when the full processing capabilities of the CPU are not necessary. Selectable using an on-chip programmable LDO voltage regulator, each level gives another incremental reduction in power consumption (see Figure 4). Developers also have the option to scale frequency to balance power and clock rate to match dynamic processing requirements.

- )) Flexible Clock Tree: Three clock sources can be configured as the main system

clock to ensure that the MCU is not running any faster than is needed to conserve power. For example, for a low power mode, a multi-speed internal clock can serve as the system clock. When extra performance is needed, the system can switch to either the High-Speed External clock (HSE) or the High-Speed Internal oscillator (HSI).

- Multispeed Internal RC Oscillator (MSI): The MSI is one of the STM32 L1's five clock options and is an ultra-low power clock that is able to generate multiple frequencies from 64 kHz to 4 MHz with power consumption proportional to speed. This is the clock the MCU uses when powering up after a reset.

- Natiomatic Clock Gating: Clock gating turns on and off downstream buses to lower the power consumption of the bus and peripherals. In addition, each peripheral can be disabled when not in use.

- Power Down Flash: With this feature, an application can run code out of RAM and disable the Flash controller, resulting in power savings on the order of 8.5%.

|                    | ADC current consumption measure (in µA) |                                      |

|--------------------|-----------------------------------------|--------------------------------------|

| CPU running at     | ADC is running in Normal Mode**         | ADC is On in Power<br>Saving Mode*** |

| 16 MHz (from HSI)  | 1453 μΑ                                 | 630 μΑ                               |

| 4 MHz (from MSI)*  | 1453 μΑ                                 | 445 µA                               |

| 1 MHz (from MSI)*  | 1000 μΑ                                 | 258 μΑ                               |

| 32 kHz (from MSI)* | 900 µA                                  | 150 μΑ                               |

\*HSI is On \*\*PDI=PDD=0 \*\*\*PDI=PDD=1

Figure 5 Rather than consume ~900 μA continuously when active, ADCs can be configured to automatically shut down after conversion for significant power savings. In this example, the ADC is in continuous mode with a delay of 15 cycles between each channel conversion.

- NADC Automatic Shutdown:

Rather than consume ~900

μA continuously when active,

ADCs can be configured to

automatically shut down after

conversion. Figure 5 shows

the impact of this feature. In

fact, with the CPU clocked at

32 kHz, the STM32 L1 can still

support a 1 MSPS sampling

rate while only drawing an

average current of 150 μA.

- Integrated RTC with Wake-Up from Low Power Modes: Essential for applications that need to wake periodically, this RTC runs out of standby circuitry separate from the main core to provide maximum standby power savings.

Which operating modes and capabilities are best to use

depends upon what CPU performance is required, which peripherals need to be active, and how fast the system has to be able to wake up. For example, it may be the case that the CPU operating at a low frequency can complete the required task before the oscillator/PLL is able to lock. For calculations with a long duration, power consumption will be better with the PLL active.

Wake time is important because all of the power consumed while waking is effectively wasted since no work is being done. For systems waking frequently, it may make more power sense to use a low power mode that wakes faster. To minimize overall wake losses, turn on system peripherals starting with those with the lowest current consumption and enable

peripherals only when they need to be used.

#### **Power Profiling**

Ideally, a low power application spends long periods in low power modes and short periods in active modes. With all of the low power features of the STM32 architecture, power consumption can be substantially improved by dynamically switching among the various power modes. However, it can be difficult to accurately determine the actual power consumption for each use case. To get the most out of a system requires a clear understanding of how the different power modes

meets its power budget will require power profiling. Power profiling, or power debugging as it is sometimes called, is not about locating explicit flaws in source code but rather uncovering opportunities to tune how the hardware is utilized. Because each use case imposes different requirements upon the MCU. developers can use profiling tools to determine which low power modes are best for each of the different operating conditions. In addition, developers can try a variety of different test cases using immediate feedback to see which approach or configuration minimizes the power profile,

Power profiling, or power debugging as it is sometimes called, is not about locating explicit flaws in source code but rather uncovering opportunities to tune how the hardware is utilized.

and other power management capabilities of the STM32 can be used. Without knowing how the system is consuming power, optimization will be difficult.

To determine whether a system

as well as to determine the maximum, minimum, and average power consumption of the final application. The power data available will also enable developers to select the optimal

## Go beyond Power Debugging!

- PowerScale measures the real power consumption – current and voltage at the same time

- ACM technology provides a wide dynamic range from 200nA to 500mA

- Easy integration to Keil ULINK

www.hitex.com/powerscale

operating frequency and voltage for each use case.

Depending upon its state, an STM32 MCU can consume currents from mAs down to a few hundred nAs. This is a huge range, and without wide monitoring resolution, power profiling will have limited accuracy and may become unusable. In addition, as soon as a debugger is connected to the system, the overall power analysis is changed due to the additional signals being used for debugging. This is why debugging is always a system intrusion in terms of power measurement.

To address this need. Hitex has implemented the energy profiling tool PowerScale which can be used independently of any debugger/compiler combination and allows for non-intrusive power profiling. PowerScale can also be integrated with 3rd party debug solutions to address the need for correlating instruction flow with energy profiling. Such an implementation has been implemented in cooperation with ARM/Keil and their ULINK®pro debug adapter. When used with the µVision Debugger, profiling can be combined with trace

events to record sleep statistics. analyze ISR execution, and perform code coverage with time execution analysis. PowerScale offers non-intrusive monitoring using up to four probes, giving developers the versatility to profile up to four different power domains. The system measures current and voltage simultaneously on all power domains and accurately correlates these measurements. This allows for a whole-system power profile that includes external components such as a Bluetooth radio, LCD, or memory IC. Supporting a large measurement range (Active Current Measurement (ACM) Probe from 200 nA to 500 mA: standard probe from 1 mA to 1 A), a time resolution of up to 100kHz, and easy adaptation, PowerScale analyzes the effects of MCU-specific power features so developers can understand the power impact of every design decision.

Similarly, developers can optimize power consumption using the J-Link debug probe from IAR Systems® which can be used to measure both board-level and chip-level power consumption (see Figure 6). For non-intrusive board-level

measurements which include the power usage of all system components, the probe is easily connected to JTAG pin 19. For MCU-level measurements, the probe can be connected to the MCU's  $V_{\rm dd}$  pins with minimal intrusiveness. The J-Link debug probe operates by sampling the program counter at a frequency up to 20 kHz and collects timestamped event information. The current power is also sampled using an ADC with a resolution of 1 mA.

These tools play an important role in quantifying the differences between different low power modes and allow developers to quantify how each system and program modification affects overall power consumption.

Common tasks to profile include the energy consumption and execution time of an interrupt handler, the actual power consumption of an ADC in each of the different modes, and which voltage scaling option provides the best power efficiency.

For more accurate results, measure power consumption over a long period of time—at least one complete cycle of the device's tasks. Since power is measured statistically, the more measurements taken and the higher the time resolution, the greater the precision. By uploading data streams over USB to a hard drive, long term measurements for statistical analysis can be made without any loss of data granularity.

Effectively unlimited recording of profile data to a hard drive enables long-term analysis of system performance. For example, a system's power profile may change if the system is hot or has been on for a long time, and profiling can expose potential problems before products are already in the field.

Both the PowerScale and J-Link tools also correlate current consumption with application code, and clicking on an event in a power graph will open the corresponding source code. This allows developers to focus their optimization effects on those code segments which consume the most power. These tools also provide valuable comparisons between the different power

saving modes to assist developers in making sure the different elements of the MCU are being used as efficiently as they can. Each tool supports multiple ways of displaying measurement data—from simple current/voltage/power graphs to more complex analysis statistics—and can be integrated with debuggers and other test tools.

This ability to quickly perform root cause power analysis by identifying any line of code responsible for a major change in power consumption enables developers to efficiently optimize power consumption by focusing on system hot spots to maximize their effort. Baselining power consumption also provides a fast means for determining if a

Figure 6 The J-Link debug probe from IAR Systems® can be used to non-intrusively measure both board-level and chip-level power consumption as well as synchronize power sampling with the MCU program counter.

These tools play an important role in quantifying the differences between different low power modes and allow developers to quantify how each system and program modification affects overall power consumption.

change in code has unintended power consequences. In addition, developers can switch out different hardware components to determine which provides better power performance. consumption. While this problem can be identified using breakpoints, the process is time-consuming and tedious. With power profiling, developers simply click on a power spike to see the cause.

The STM32 architecture utilizes a flexible, multi-channel DMA engine capable of transferring data between peripherals and/or memory with minimal involvement of the CPU. The CPU can even be put into sleep mode during DMA transfers to further improve power efficiency.

Power profiling can also help identify mismanagement of peripherals. For example, a peripheral may be accidentally left on after being used by a specific function. Such an oversight can be quickly recognized and resolved by noting that the idle power is several mA higher than the expected baseline. Alternatively, an event such as an external signal occurring more frequently than originally specified may wake the system prematurely and adversely increase power

#### Power Efficient Design

A key component of power efficiency is processor performance given that the faster the MCU can perform a task, the sooner it can return to sleep. The Cortex-M foundation of the STM32 architecture was specifically designed for the real-time processing needs of embedded systems. Its Thumb2 instruction set brings 32-bit performance with 16-bit code density, and combined with other

enhancements like an integrated interrupt controller, single-cycle multiply functionality, and dedicated instruction and data buses, the Cortex-M architecture provides a 30% performance improvement over the ARM7TDMI architecture, allowing applications to reduce active time and improve power efficiency.

For example, consider an application requiring 20 DMIPS. An ARM7TDMI running at 22.2 MHz will consume 8.7 W while a Cortex-M3 running at 16.7 MHz will consume only 2.5 W. The result is that the Cortex-M3 requires 25% less speed and consumes 70% less power.

For additional CPU offloading, the STM32 architecture utilizes a flexible, multi-channel DMA engine capable of transferring data between peripherals and/or memory with minimal involvement of the CPU. The CPU can even be put into sleep mode during DMA transfers to further improve power efficiency. With its dual APB architecture. peripherals can also be clocked independently. To speed memory transactions, the Cortex-M core supports Atomic Bit Manipulation (ABM). Traditionally, adjusting

a bit in RAM or a peripheral requires a read/modify/write sequence. ABM uses aliases to enable single-instruction reading and writing, resulting in performance and power savings.

With much of a system's functionality implemented in software, application developers can improve power efficiency beyond optimizing how fast processing is completed and the MCU can return to sleep. The STM32 architecture, and EnergyLite STM32 L1 MCUs in particular, provide a variety of low power modes and integrated circuitry such as dynamic voltage scaling, flexible clocking system with automatic clock gating, the ability to turn off Flash, and fast timeto-wake. Through the use of power profiling tools like J-Link and PowerScale, developers can focus their optimization efforts on power hot spots within the system as well as quickly identify and resolve unexpected power spikes. In this way, developers can meet the changing performance and responsiveness requirements of their application while achieving the optimal operating configuration for every case. 💝

# Simplifying Embedded Design for Accelerated Time-to-Market

By Alec Bath, Applications Engineer, STMicroelectronics

Designing an efficient, real-time embedded system requires that each component has been optimized to operate in conjunction with the rest of the system. Today's MCUs accelerate system design by integrating many of the components an application requires and managing their interactions with an efficiency not possible when using external components.

The high level of intelligent integration in the STM32 family, for example, speeds time-to-market by enabling:

- Greater performance through coordination of all system components

- )) Elimination of throughput bottlenecks with a multi-layer bus interconnect

- )) Increased responsiveness and determinism by offloading tasks from the CPU to reduce interrupts

- Simplification of design through flexible clocking and interface options

- )) Increased system safety through self-monitoring

- Lower system cost by reducing component cost and system complexity

# Greater Performance through Coordination

As embedded MCUs become more complex, their internal architectures can give rise to bottlenecks which can impede system performance. For example, executing code from embedded Flash can reduce an MCU's maximum performance because of wait states imposed by the Flash controller. Similarly, embedded accelerators may be unable to keep up with the MCU core, thus slowing system performance when their capacity is tapped. The result is that performance often degrades at higher core frequencies.

Architectures designed to compensate for known system bottlenecks can eliminate their negative impact on performance. For example, the STM32 architecture avoids losses in performance as core frequency increases through the use of Adaptive Real-Time (ART) memory accelerator technology.

The ART Accelerator introduces a prefetch queue and branch cache between the embedded Flash and CPU core. Each time an event such as a subroutine call, interrupt, or conditional branch occurs and breaks the linear execution of the code, the ART Accelerator checks if this event has already been

Figure 1 Integrated architectures can eliminate system bottlenecks by coordinating interactions between system components. For example, the ART Accelerator of the STM32 architectures buffers first instructions and constants so they can be placed into the prefetch queue to eliminate any performance losses associated with branching when executing from Flash.

stored in the cache (see Figure 1). If so, the first instructions and constants associated with this branch can be immediately pushed from the branch cache to the prefetch queue, thus eliminating any performance losses associated with branching. If the event has not vet been stored and its first instructions are not available. they are now stored in the buffer to prevent any delay the next time this event occurs. With a deep branch cache, most applications achieve performance equivalent to zero wait states when executing from Flash.

Figure 2 shows the impact of ART Accelerator technology on MCU performance when the MCU operating frequency reaches a point where the Flash becomes a bottleneck and imposes losses which can represent a significant percentage of overall performance. By eliminating these losses, the ART Accelerator provides consistent performance that scales linearly with core frequency. As can be seen, the STM32 F4 is able to provide its full 210 DMIPS performance at 168 MHz when executing from Flash.

Figure 2 Flash bottlenecks that arise as operating frequency increases can represent a significant percentage of overall performance. By eliminating these losses, the ART Accelerator provides consistent performance that scales linearly with core frequency, allowing the STM32 F4 to provide its full 210 DMIPS performance at 168 MHz when executing from Flash.

With the increase of digital processing in embedded systems, whether for motor control, decoding of digital content, or high speed interfaces, MCUs need to move significantly more data than they have in the past.

The ART Accelerator is an excellent example of an architectural enhancement which is only possible when an MCU is highly integrated. Eliminating the wait states associated with branching requires intimate coordination between the Flash controller and the instruction pipeline. When multiple architectural enhancements like the ART Accelerator and those described below are combined in an MCU, the improvements in performance are tremendous.

#### Multi-layer Bus Interconnect: Data Transfers without Involving the CPU

An essential element of a highly integrated MCU is its internal interconnect bus. With the increase of digital processing in embedded systems, whether for motor control, decoding of digital content, or high speed interfaces, MCUs need to move significantly more data than they have in the past. The interactions between the CPU, numerous accelerators, peripherals, and high-speed data interfaces can severely stress an MCU's

bus. Developers must be able to account for worst-case operating scenarios when multiple peripherals and interfaces are active at the same time, and how the bus is architected determines the overall level of contention and latency in the system.

With the myriad peripherals in a highly integrated MCU, a simple interconnect will not suffice; rather, a bus matrix which enables independent connections between masters and slaves is required. Figure 3 shows the 7-layer matrix that interconnects the STM32 F4 to enable seamless and efficient operation of the core and multiple peripherals simultaneously. Bus masters (shown along the top) include the CPU, the 2 DMA controllers, and the Ethernet and USB interfaces. Slaves, shown on the right, include the Flash memory through the ART Accelerator, 2