# STM32 Journal

Volume 1, Issue 2

### In this Issue:

- >>> Developing High-Quality Audio for Consumer Electronics Applications

- >>> Bringing Floating-Point Performance and Precision to Embedded Applications

- >> Achieving Ultra-Low-Power Efficiency for Portable Medical Devices

- )) Accelerating Time-to-Market Through the ARM Cortex-M Ecosystem

- >>> Introducing a Graphical User Interface to Your Embedded Application

### We Are Not Alone

By Nicholas Cravotta, Technical Editor

**Table of Contents**

Volume 2, Issue 2

- 2 Editorial

- 3 Bringing 32-bit Performance to 8- and 16-bit Applications

STM32 Journal

- 11 Developing High-Quality Audio for Consumer Electronics Applications

- 19 Bringing Floating-Point Performance and Precision to Embedded Applications

- 26 Achieving Ultra-Low-Power Efficiency for Portable Medical Devices

- 34 Accelerating Timeto-Market Through the ARM Cortex-M Ecosystem

- 42 Introducing a Graphical User Interface to Your Embedded Application

When I got my first paycheck as an engineer nearly three decades ago, coding and layout weren't exactly social activities. While there was a certain amount of team collaboration to decide what I would work on, the majority of what I did was by myself. When I decided to shed the ten pounds I had gained as a freshman, it was a similar story. I never found someone willing to go consistently to the gym with me, so I pressed those weights alone as well.

It's quite a different world today. Take at look at the Nike+ FuelBand on the cover of this issue's STM32 Journal. Worn on your wrist, it records your every activity, not just when you're on the treadmill.

What makes the FuelBand such a ground-breaking product is how it brings people together. It doesn't matter whether you work out at 2am or are in a strange city on travel, with this next-generation exercise monitor, you are never alone. Connected to your phone via Bluetooth, you can be in touch with exercise buddies all around the world through the Nike+ online community.

The Nike+ FuelBand is guite a feat of engineering. To differentiate between simple gestures and active motions requires complex signal processing capabilities. The device must also be constantly on since even vou don't know when you might jump into action. 120 LEDs comprise the display and "Fuel" indicator, and the device can operate for up to four full days without recharging. It also weighs less than one ounce, including the batteries. Now that's an efficient design.

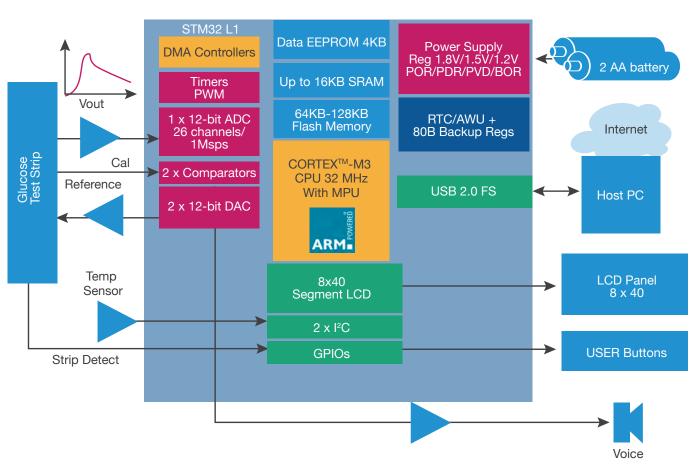

At the heart of the FuelBand is ST's ultra-low power STM32 L1 microcontroller. In addition to providing the 32-bit performance and processing capacity required for advanced signal processing, the STM32 architecture offers the real-time responsiveness, power efficiency, and highly integrated peripherals and memory required for even the most demanding embedded applications. With innovations like FuelBand and Nike+ technology, Nike has leveraged social networking to change the way we live together. Exercise, as a result, is no longer a solo endeavor.

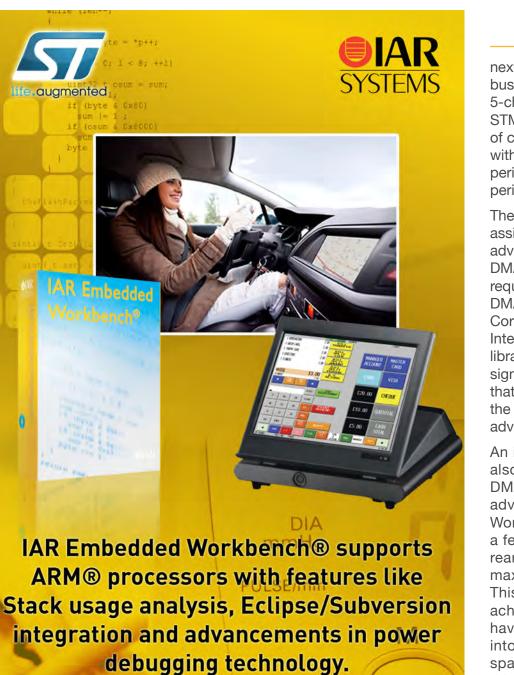

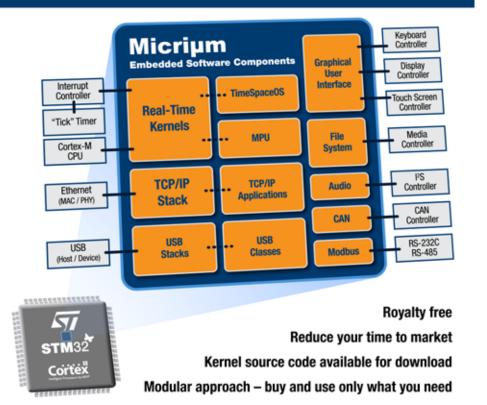

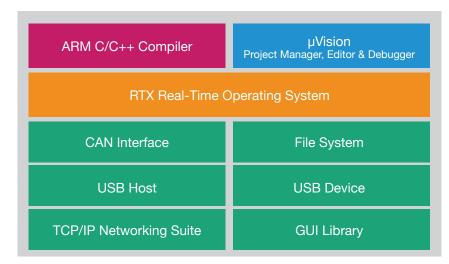

Neither, it turns out, is engineering. The network supporting the STM32 architecture enables a whole new level of collaboration. Design tools from companies like Keil, IAR Systems, and Micrium are like having a team of experts sitting right next you. Need to extend a design by adding audio or a capacitive touch GUIbased interface? Just call upon partners like DSP Concepts and GeeseWare. And with the STM32 architecture based on the ARM Cortex-M0, M3, and M4 cores, you have access to a global ecosystem second to none. You can even ask questions of your fellow engineers at 2am or share your own hard-won experience through forums, blogs, and tweets.

It truly is a different world we live, play, exercise, and work in.

### Bringing 32-bit Performance to 8- and 16-bit Applications

By Reinhard Keil, Director of MCU Tools, ARM Germany GmbH Shawn Prestridge, Senior Field Applications Engineer, IAR Systems Sean Newton, Field Applications Engineering Manager, STMicroelectronics

Today's embedded applications are being called upon to provide an increasing number of capabilities. More and more devices need to be connected, require greater precision, must offer a graphics-based interface with touch capabilities, utilize sophisticated signal processing, and support multimedia playback.

In the past, developers were compelled by cost constraints to base their designs on 8- and 16-bit architectures that limited performance. Now, with the availability of next-generation MCUs like the STM32 F0 that provide 32-bit performance at 8-bit budget pricing, OEMs can bring substantial value to end-users without having to compromise functionality. In addition, powerful development tools like Keil's MDK-ARM and IAR Embedded Workbench enable developers new to 32bit programming to immediately exploit the full capabilities of the STM32 F0 architecture.

### The 32-bit Advantage

There are several ways in which the STM32 F0 lowers product cost compared to 8- and 16-bitbased designs. Specifically, because these MCUs tend to be based on legacy architectures, they have many limitations that slow development by forcing designers to work around the architecture, so to speak. For example, to complete a 16 x 16 multiplication for a processing algorithm, a 16-bit CPU requires four multiplies and several additions, depending upon the implementation. An 8-bit CPU would require significantly more cycles. With the STM32 F0, this takes a single instruction.

The result is code that makes better utilization of MCU resources, leading to faster operation, more performance per MHz, higher code density, and greater power efficiency. Since each instruction does more per clock cycle, applications can be written using less code. In addition to accelerating development, shorter code is easier to debug as well. Together, all of these benefits lead to lower system cost.

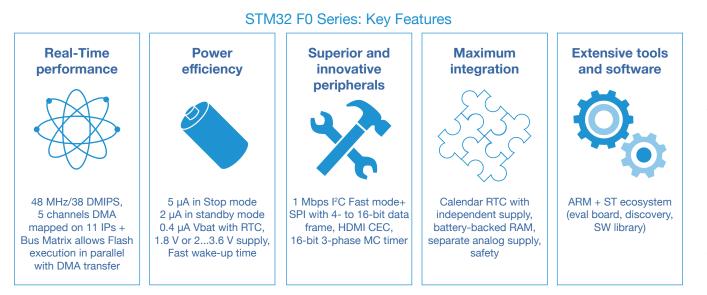

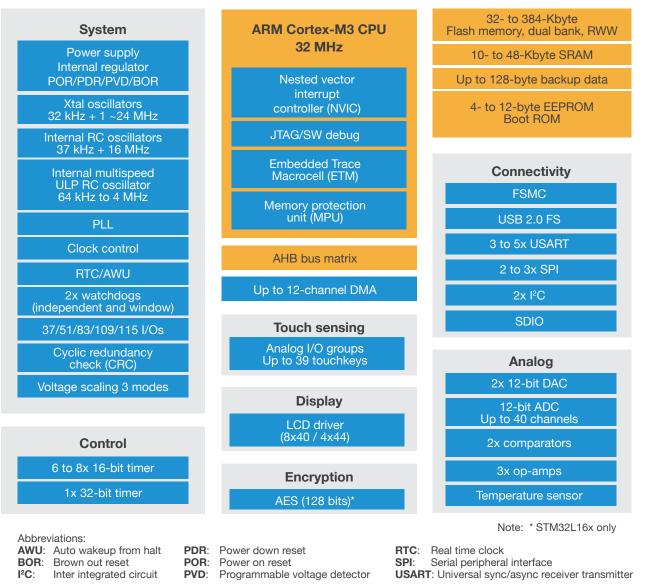

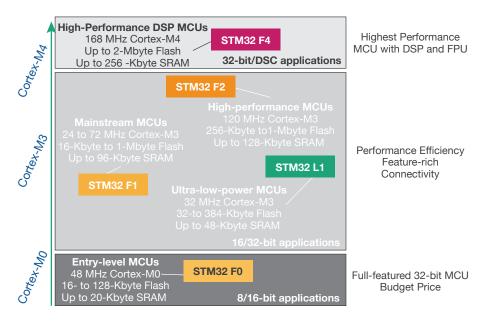

Cost, however, is only one of the numerous advantages the STM32 F0 has over 8- and 16bit architectures. The STM32 F0 is a full embedded MCU built using the same STM32 DNA that the rest of the STM32 family has, including excellent real-time performance, DMA, high-resolution ADC and DAC peripherals, motor control timers, and connectivity interfaces. These integrated capabilities bring tremendous efficiency to cost-sensitive designs in a way that limited 8- and 16-bit MCU architectures cannot (see Figure 1).

For example, the availability of a 32-bit bus not only speeds data transfers and increases computing performance, it improves system reliability. Consider the challenge of reading a 12-bit DAC using an 8-bit bus where the CPU has to read the DAC twice to capture the entire sample. If an interrupt occurs between these reads, the DAC data may be overwritten by the next sample before the interrupt is completed and the second read can be executed. To prevent this, developers have to manually disable interrupts for every such "atomic" operation in an application. If even one instance is missed, this creates a potential for an intermittent error that will be extremely difficult to resolve.

### DMA: Moving Data Efficiently

The STM32 F0 is a modern architecture integrating the

#### STM32 F0 series L1, F0, F1, F2, F4 series: seamless migration amongst 300 pin-to-pin compatible part #s

Figure 1 The STM32 F0 is a full embedded MCU built using the same STM32 DNA that the rest of the STM32 family has and offers tremendous efficiency to cost-sensitive designs in a way that limited 8- and 16-bit MCU architectures cannot.

latest in processing, power, and debugging technology. For example, multiple low power modes extend greater control over power consumption to achieve longer operating life for battery-operated and portable devices. In addition, the STM32 F0 offers advanced features, including full Direct Memory Access (DMA) and the ability to shut down the ADC between samples to further increase performance while lowering power consumption. In general, 8-bit MCUs don't have the powerful peripherals that higher performance MCUs tend to have. For example, DMA has become an essential peripheral for applications that need to move a great deal of data, whether as part of a processing algorithm, receiving data from an interface, playing back audio, or transferring graphics to the display. In a traditional 8-bit architecture, each word of data has to be moved by the CPU. In addition,

pointers need to be updated and a loop managed. Thus, every 8-bits of data takes several cycles of CPU time to move.

With the DMA in the STM32 F0, an entire block of data can be moved without involving the CPU. After the program configures the transfer, the DMA manages moving the data in the background. In fact, the CPU can drop into a low power sleep mode while it waits for the transfer to complete. As a result, data transfers do not consume unnecessary CPU cycles and require less power to complete than for 8- and 16-bit architectures.

The availability of a DMA controller can also greatly simplify and accelerate product development. Consider reading data off of a high-speed data interface such as I2C. Because of the load on the CPU, 8-bit developers have to work around the MCU's architecture, using many interrupts to utilize the time between data reads. With the STM32 F0, the CPU operates independently of the interface, allowing developers to program the CPU for other tasks without having to worry about missing an interrupt or losing data.

Because the STM32 architecture uses an internal bus matrix, the DMA can be used in conjunction with each of the different onchip memories as well as many of the peripherals. For example, the DMA can be configured to sample the ADC regularly over a period of time: a timer triggers the DMA to read the ADC and store the result in memory without involving the CPU. Once the operation is complete, the ADC shuts down until the

www.iar.com

next sample time. In fact, the bus matrix combined with a 5-channel DMA enables the STM32 F0 to support execution of code from Flash in parallel with other memory-memory, peripheral-memory, or memoryperipheral DMA transfers.

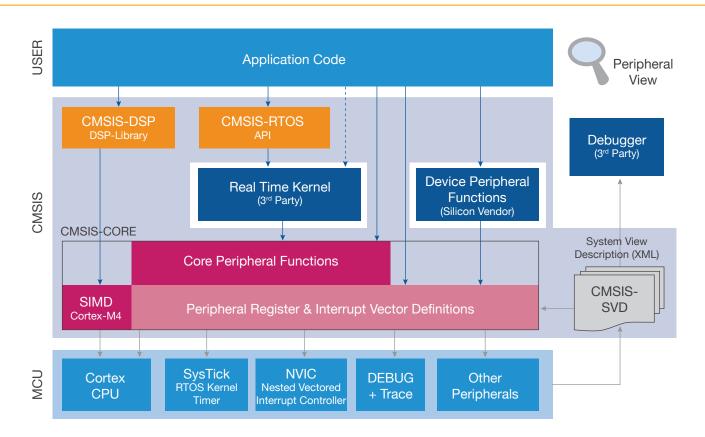

There are many tools to assist developers in taking advantage of the STM32 F0's DMA capabilities without requiring them to become DMA experts. The ARM DSP Cortex Microcontroller Software Interface Standard (CMSIS) library, for example, provides signal processing functionality that has been optimized for the STM32 F0 and takes full advantage of the DMA.

An intelligent compiler can also help developers exploit DMA technology to its fullest advantage. IAR Embedded Workbench, for example, offers a feature that will automatically rearrange program data to maximize the use of the DMA. This enables developers to achieve high efficiency without having to put much forethought into how to layout the data space. The compiler achieves this by analyzing how data is used by the application. Consider a program that copies two different data structures using DMA. Each copy operation requires a separate DMA operation. However, after the compiler collocates the data structures in memory, they can be copied with a single DMA transfer.

Note that each MCU may use the DMA in a slightly different manner. Keil's MDK-ARM, for example, abstracts how the DMA is used from the application through an API that prevents code from being tied to a particular processor. This enables developers to migrate applications to other STM32 devices and know that code utilizing the DMA will still perform optimally.

### Writing 32-bit Code

Moving from 8-bit to 32-bit assembly is not trivial, given the vastly different instructions 32-bit architectures offer; i.e., single-instruction, multiple data (SIMD) instructions work on multiple data to vastly accelerate processing. Even moving between 16-bit architectures is challenging given that the peripherals can differ and impact how application code is written.

|        | Benchmark<br>Application | 8-bit N      | <i>l</i> lath | 8-bit N     | /latrix | 8-bit S <sup>r</sup> | witch | 16-bit       | Math | 16-bit l    | <i>M</i> atrix | 16-bit S    | Switch | 32-bit       | Math | Floating<br>Ma |             | Mat<br>Multipli |      | FIR f        | filter |

|--------|--------------------------|--------------|---------------|-------------|---------|----------------------|-------|--------------|------|-------------|----------------|-------------|--------|--------------|------|----------------|-------------|-----------------|------|--------------|--------|

| 16-bit | MSP430                   | 178          | 8             | 86          |         | 198                  |       | 126          |      | 90          | )              | 198         |        | 222          |      | 1102           |             | 136             |      | 98           | 30     |

|        | dsPIC                    | C 236        |               | 420         |         | 424                  |       | 22           | 4    | 552         |                | 424         |        | 424          |      | 2020           |             | 464             |      | 22           | 56     |

|        | PIC24 236                |              | 42            | 0           | 416     |                      | 224   |              | 552  |             | 416            |             | 424    |              | 2020 |                | 464         |                 | 22   | 56           |        |

|        | H8/300H                  | 3/300H 344   |               | 412 444     |         | 4                    | 352   |              | 482  |             | 478 574        |             | 4      | 1104         |      | 482            |             | 13              | 92   |              |        |

|        | MaxQ20                   | 230          |               | 252         |         | 192                  |       | 204          |      | 328         |                | 184 288     |        | В            | 1172 |                | 398         |                 | 1478 |              |        |

|        | HCS12                    | 12 83        |               | 188         |         | 162                  |       | 76           |      | 262         |                | 174 32      |        | 32           | 3    | 2082           |             | 219             |      | 1917         |        |

|        | ATxmega64A1              | mega64A1 118 |               | 398         |         | 338                  |       | 174          |      | 490         |                | 350 300     |        | 0            | 1080 |                | 584         |                 | 1362 |              |        |

|        | ARM7TDMI                 | 636          |               | 392         |         | 452                  |       | 636          |      | 396         |                | 452         |        | 620          |      | 1832           |             | 428             |      | 1528         |        |

| 8-bit  | 8051                     | 233          |               | 398         |         | 305                  |       | 452          |      | 50          | 4              | 49          | 3      | 90           | 9    | 219            | 90          | 53              | 6    | 20           | 56     |

|        | PIC18F242                | 170          |               | 324         |         | 208                  |       | 286          |      | 692         |                | 282         |        | 542          |      | 1400           |             | 676             |      | 2006         |        |

|        | ATmega8                  | 134          |               | 354         |         | 350                  |       | 198          |      | 43          | 4              | 38          | 2      | 34           | 2    | 108            | 38          | 49              | 0    | 13           | 58     |

|        | M32 F0                   | Speed        | Size          | Spood       | Size    | Spood                | Size  | Spood        | Sizo | Spood       | Size           | Spood       | Size   | Spood        | Sizo | Spood          | Sizo        | Spood           | Size | Spood        | Siz    |

|        | npiler Option<br>le Size | Speed<br>110 | 94            | Speed<br>68 | 512e    | Speed<br>98          | 120   | Speed<br>114 | Size | Speed<br>68 | 51Ze           | Speed<br>98 | 120    | Speed<br>112 | Size | Speed<br>640   | Size<br>636 | Speed<br>268    | 84   | Speed<br>550 | 55     |

Figure 2 The STM32 F0 delivers substantial code size reduction when comparing to other 8/16 architectures. This grid show the code size in bytes for various benchmark applications. Source: Benchmark applications and results for 8/16-bit: TI MSP430 Competitive Benchmarking (www.ti.com/lit/an/slaa205c/slaa205c.pdf). STM32 F0 code generated with MDK V4.23, MicroLib, and compiler optimization for execution speed or code size.

The STM32 F0 architecture facilitates a smooth migration to 32-bits. The ability to develop in embedded C reduces the learning curve of moving to a new architecture. In many cases, engineers are already familiar with the ARM Cortex-M architecture. Developers can further ease migration by using a tool chain they are already familiar with, such as IAR Embedded Workbench and Keil's MDK-ARM. Finally, developing for the STM32 F0 is simplified through the use of the ARM CMSIS libraries that abstract much of the underlying hardware from the application.

Moving to the STM32 F0 will result in a substantial reduction in code size because of the density possible with 32-bit instructions, on the order of 30% (see Figure 2). With its 32-bit address space, the STM32 F0 also eliminates addressing and paging limitations that complicate memory management in 8-bit designs. For example, data sets can be larger than a single page and there are no longer "far" addressing penalties. The use of object-oriented constructs, as is common with modern programming and modeling tools, can also be implemented without disruptive fragmentation.

Without question, the best compiler is the human brain. Given enough time, a person can create a highly optimized program that no compiler can beat. Programming in assembly can also be more efficient than a C version of the same program. Time, however, is one of the resources of which developers don't have a surplus. In addition. hand-written code can be extremely fragile; if the product specs change in a material way, many of a programmer's optimizations will need to be completely reevaluated.

The reality is that Keil's MDK-ARM and IAR Embedded Workbench are smart enough to make excellent coding choices that might take a person weeks to evaluate. For example, how data is laid out impacts performance. There's also the challenge of balancing optimization techniques like

loop unrolling to memory footprint. A compiler can make these decisions for an entire program in just minutes. Each of these tools offers numerous optimization options it can perform automatically for the STM32 F0 architecture that are significantly different than those typical with 8- and 16-bit MCUs. These options include data-flow optimizations such as common sub-expression elimination and loop optimizations such as loop combining and distribution. They also include advanced techniques like branch speculation and executing code out of sequence.

These development tools for the STM32 F0 give excellent results. Compiler efficiency compared to human coding has been estimated at 97%. Put another way, the cost of achieving that last 3% is on the order of weeks to months of development time. In addition, if a major design change is required, the compiler can complete a new set of optimizations with just a simple recompile.

As a modern architecture, the STM32 F0 is supported by similarly modern tools that

utilize the latest advancements in compiler, debugger, and middleware technology to reduce development time and effort considerably. Being based on the Cortex-M architecture. the STM32 F0 is backed by a larger ecosystem of tools and production-ready software than any other MCU architecture on the market. In addition, for many applications where the code base is small, the tools may be effectively free. For example, both IAR Embedded Workbench and Keil's MDK-ARM are free when used for programs under 32 KB, thus enabling 32-bit design with a low initial investment.

### Advanced Debugging

While the ability to design demanding applications quickly is important, developers need debugging capabilities that can abstract the complexity of applications while still providing full visibility and control during run-time operation. In addition, many embedded markets, including medical and industrial, require that application software be certified as well.

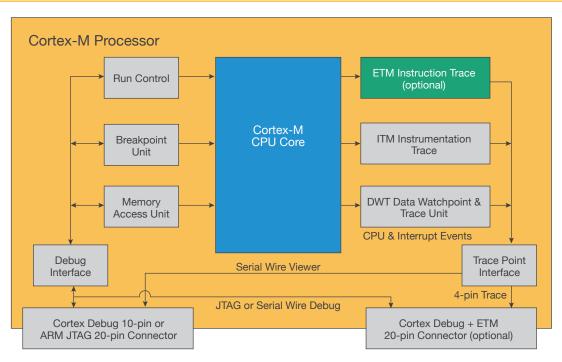

The integrated debug capabilities of the STM32 F0 provide many advanced capabilities that offer a superior debug experience compared to old-fashioned 8- and 16-bit architectures. For example, the STM32 F0 architecture features ARM's Coresight technology to help developers analyze, optimize, and verify program execution with minimal effort and cost.

Coresight represents the latest in advanced debugging technology. Traditional MCUs offer only limited run/stop debug capabilities. To achieve greater visibility, an in-circuit emulator on the order of \$1000s may be required, and a different pod will be required for each MCU in use. A few of the benefits Coresight provides which other MCU architectures do not include on-the-fly read/write access and trace capabilities at the instruction, data, and application level. As implemented in the STM32 F0, Coresight also supports up to 4 hardware breakpoints and 2 watchpoints without requiring the use of intrusive monitoring techniques that can skew performance.

Developers also have a choice of many low-cost debug adapters for the STM32 F0. For example, the STLink in-circuit

# STM32® FO budget price with superior analog and control peripherals

STM32 Releasing your creativity

For further information, visit www.st.com/stm32f0

debugger and programmer, which links the STM32 F0 target board to a PC via USB, is \$25. For more advanced debugging, IAR Systems has the I-Jet debugger while Keil offers developers its ULINK2 and ULINKpro debuggers.

These debuggers offer powerful capabilities that are often not available for 8- and 16-bit designs. Keil MDK-ARM tools, for example, enable comprehensive code coverage, execution profiling, and performance analysis to ensure maximum performance efficiency. With the I-jet debugger, IAR Systems is able to offer non-intrusive power consumption monitoring at the board- and chip-level. Such "power debugging" enables developers to uncover opportunities to utilize and tune hardware to achieve the highest power efficiency.

### STM32 F0 Features

STM32 F0 MCUs have been designed with real-time operating system (RTOS) and kernel support in mind to enable much tighter integration with RTOSes like Keil's royaltyfree RTX. In a typical 8- or 16-bit MCU, for example, the RTOS and application share the stack, and complex nesting problems can arise that overflow the stack and crash the system. The only way to avoid such issues is to overprovision the stack. The STM32 F0, in contrast, has two stacks: one for the application and one for the RTOS. This prevents applications from compromising RTOS integrity. In addition, RAM overhead is much lower.

Other companies basing MCUs on the Cortex-M0 architecture integrate only the minimum capabilities an MCU requires. ST is the only company to offer Cortex-M0-based MCUs with:

- )) Easy Communication: Using the integrated DMA controller, the STM32 F0 can support continuous I<sup>2</sup>C at a rate of 1 Mbps without bogging down the CPU. This data rate isn't possible to achieve on an 8or 16-bit MCU that does not support DMA.

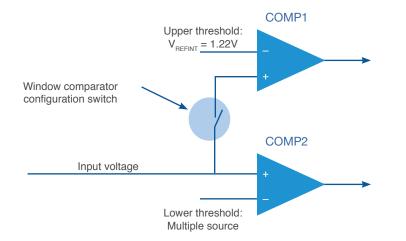

- Advanced Digital and Analog Capabilities: The STM32 F0 integrates a wide range of IP to facilitate the design of sensing and control systems. For example, advanced timers enable the accurate output

of complex AC waveforms. On-chip comparators simplify the design of sensors. The 12-bit, multi-channel ADC operating at up to 1 MSample/s allows for fast and precise data acquisition, as well as improves system responsiveness to external events. Advanced timing control is enabled using the 32-bit and 16-bit PWM timers with 17 capture/compare I/O mapped onto up to 28 pins.

)) Safety Ready: With shrinking process technologies and larger memories combined with frequently changing data, bit errors from cosmic ravs can occur. For systems that must meet stringent safety compliance standards, the STM32 F0 performs realtime, hardware-based RAM parity checking and 16-bit CRC verification for Flash to ensure the integrity of memory. RAM checks are performed automatically whenever memory is accessed. Flash verification is self-managed, enabling developers to confirm program integrity upon startup and when updating firmware to verify that no bits have been flipped since they were written.

### **Double Sourcing**

In recent years, the industry has seen shortages when devices are manufactured in a single location. To ensure its customers will always have uninterrupted access to product, ST employs a double sourcing strategy in which all STM32 devices are manufactured in at least two fabs in different parts of the world. This prevents product supply from being vulnerable to environmental factors that shut down a particular production fab. It also enables ST to meet any unanticipated rise in demand more easily by shifting production among multiple fabs.

**Reliability:** The STM32 F0 integrates two watchdog timers, one of which is a windowed watchdog timer. These timers, which can operate in low power modes as well, provide a higher level

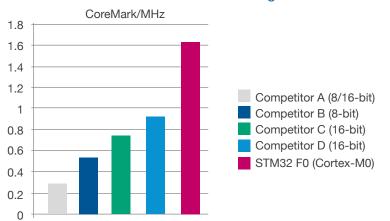

STM32 F0 Benchmark Positioning

Figure 3 The STM32 F0 provides an optimal balance of cost, performance, and peripherals for embedded applications.

of reliability not available in most 8- and 16-bit MCUs. A Clock Security System (CSS) enables systems to switch to internal RC-based clocking in case of external clock failure to ensure systems can shut down gracefully rather than catastrophically.

### **)) Optimized Communications:**

The STM32 F0 supports the HDMI Consumer Electronics Communication (CEC) protocol. Important for devices targeted for consumer markets, this peripheral enables devices to have smart control over multiple HDMI lines. For devices needing remote control capabilities, ST provides a full infrared firmware library.

- )) Memory: Memory capacity ranges from 16 KB to 128 KB Flash

- )) 1.8V Ready: The STM32 F0 can interface directly to 1.8 to 3.6 V-based devices. This eliminates the need for additional conditioning circuitry 8- and 16-bit MCUs require.

Description: Sensing: To add touch to 8- and 16bit MCU-based designs, a second processor is typically required. With the STM32 F0, developers can easily introduce capacitive touch sensing to applications, with up to 18 keys and slider/wheel configurations, all with a single chip. In addition, touch sensing can be implemented with zero CPU loading when using the charge transfer method.

Overall, the STM32 F0 provides an optimal balance of cost, performance, and peripherals for embedded applications (see Figure 3). Rather than tie developers to a proprietary architecture with limited tools and support, ST offers the industry's widest Cortex-M portfolio with more than 300 compatible devices across the entire STM32 family.

With code-, pin-, and peripheralcompatibility across the STM32 family, developers can leverage Cortex-M0-based designs to M3- and M4-based MCUs with unparalleled flexibility. For example, applications designed using the STM32 F0 are easily migrated to the STM32 F2 and STM32 F4. With Keil's MDK-ARM and IAR Embedded Workbench, developers just need to change the MCU selection and the compiler handles all of the details by recompiling the code. This enables developers to easily migrate to an MCU with more performance, memory, and peripherals without rewriting the application. As a result, developers can leverage the same application and tool chain across an entire product line and a variety of MCUs.

Similarly, developers have the option of designing code on the STM32 F2 or F4 with the intention of later downsizing to the STM32 F0. This enables design to take place on a platform with the highest performance and memory to accelerate proof-of-concept design. Once the design has settled, developers can optimize it for the STM32 F0.

With the STM32 F0, ST offers a compelling alternative to 8- and 16-bit devices. For the same price, developers get more performance, higher resolution peripherals, better tools, wider support, accelerated development, and faster time-to-market. To explore how the new STM32 F0 can bring the benefits of 32-bit technology to your designs, the STM32 F0 Discovery Kit is available now for less than \$10.

### Developing High-Quality Audio for Consumer Electronics Applications

By Paul Beckmann, CEO/CTO, DSP Concepts Dragos Davidescu, Chief System Architect, STMicroelectronics John Knab, Application Engineer, STMicroelectronics

With the falling cost of high-performance MCUs, manufacturers are considering adding digital audio functionality to more and more consumer devices and other embedded applications. Their goal is to support the wide variety of media sources users want to access such as an iPhone, Internet radio, external USB devices, and SD cards.

Achieving high-quality sound output, however, is nontrivial. Sound quality depends greatly upon the final system configuration, making it difficult to design even when prototype hardware is available. In addition, implementing realtime digital signal processing algorithms introduces a whole new set of concerns for developers used to MCUbased design. These include implementing advanced filters and processing algorithms,

handling fixed-point issues, using DSP-like instructions, and optimizing complex algorithms for speed, MIPS, memory, and power.

In this article, we'll show how developers can leverage MCUbased digital signal processing (DSP) and floating-point unit (FPU) capabilities to enable real-time audio playback, implement enhanced algorithms. convert between multiple clock domains, manage highspeed communications without impacting audio guality, optimize designs to balance quality and cost, and manage other system tasks such as a graphical user interface, all with a single microcontroller.

### **Consumer Audio**

Traditionally, introducing audio to an embedded application requires digital signal-processing capabilities beyond the capabilities of most MCUs. Even a "simple" product like an iPod speaker dock requires a significant number of advanced audio algorithms to achieve full performance:

#### Spatial enhancement: In

an iPod docking station, the speakers may be only 12-18 inches apart. To create a more spacious, rich sound, spatial enhancement is required is to compensate for the close proximity of the speakers.

#### Multi-channel audio: For

systems supporting more than two speakers, the stereo input signal requires processing to create the additional audio channels.

**Equalization:** Speakers need to be equalized to achieve better sound quality. If the speakers in use change, the equalization needs to be adjusted as well. Developers can employ a variety of equalization methods, including graphic and parametric equalization. For higher-end applications, developers may even want to design their own equalization algorithms using a tool like MATLAB.

**Peak limiting:** Speakers exhibit nonlinearity at louder sound levels. By applying a time-varying gain and carefully controlling the peak levels, the system can play louder with a minimum amount of distortion.

**Boost:** When listening to music at low volume levels, much detail, and therefore depth, can be lost. Boosting of the bass and certain other frequencies at low volume levels using loudness compensation or perceptual volume-control techniques can significantly improve perceived sound quality.

**Level matching:** Level matching eliminates the need for users to adjust the volume for each song

when shuffling through a large library of albums.

Digital audio has commonly been implemented in consumer electronics and embedded applications using a second processor dedicated to this task. To meet market cost pressures, however, manufacturers need to be able to process audio on the host CPU.

In general, it is easier to implement audio on an MCU than it is to implement real-time responsiveness and connectivity on a DSP. DSPs, while excellent at processing audio, don't have the peripherals or interrupt responsiveness required for realtime systems. DSP architectures are also typically designed for high-end signal processing and massive parallelism that exceeds the requirements of the typical consumer application. In addition, DSPs are not designed to support communication interfaces like USB. SD cards, or Wi-Fi, so a DSP-based docking station would still require a second processor to handle connectivity.

With the introduction of DSP capabilities to MCU instruction sets, MCUs now have the advanced math processing

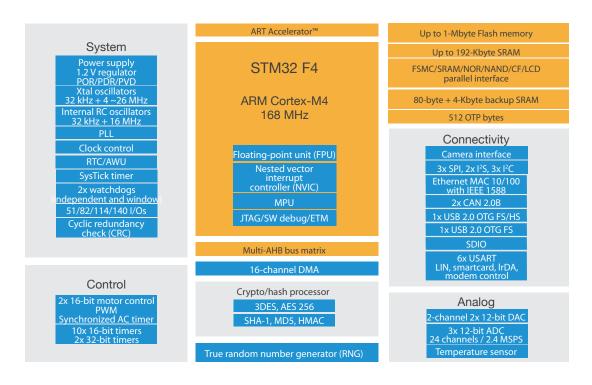

Figure 1 ST has expanded its STM32 MCUs beyond the base Cortex-M architecture with a variety of integrated peripherals to create a wide range of MCUs that optimize performance, memory, and cost for nearly every embedded application.

capabilities required to handle not only basic audio processing but the advanced algorithms required to improve quality as well. In addition, rather than requiring developers to handcode assembly as is typical for DSP-based designs, MCUs offer ease-of-use and faster time-tomarket through C programming and application libraries. MCUs are also specifically architected to provide short and deterministic interrupt latency as well as ultra low-power operation for battery-powered applications.

### The STM32 MCU + Audio Architecture

The STM32 architecture from ST has been designed to bring 32-bit MCU capabilities to a wide range of consumer audio applications, including multimedia speakers, docking stations, and headphones. The STM32 F4, based on an ARM Cortex-M4 core operating at up to 168 MHz, also integrates capabilities such as DSP instructions and a floating-point unit to allow manufacturers to produce consumer audio applications offering quality playback at the lowest cost (see Figure 1).

## Accelerating Audio Product Development

### Announcing Audio Weaver support for the STM32 F4

Reference designs for USB audio, multimedia speakers, headphones, and docking stations

www.dspconcepts.com

DSP application example: MP3 audio playback

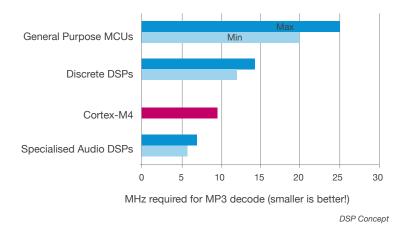

Figure 2 With its Cortex-M4 core, the STM32 F4 offers excellent audio processing capabilities that exceed the performance of many general-purpose MCUs and discrete DSPs.

The STM32 F4 offers excellent audio processing capabilities (see Figure 2). With its rich peripheral integration, a single STM32 F4 can provide a costeffective, single-chip solution for implementing embedded audio that combines performance, ease-of-use, connectivity, and signal processing to achieve quality audio playback. Key capabilities of the STM32 F4 for accelerating audio design, enhancing performance, and lowering system cost include:

### **Digital Signal Processing Instructions:** With the STM32

F4, developers have access to up to 105 DSP-specific instructions. These instructions include single-cycle multiplyand-accumulate (MAC), saturated arithmetic, and both 8- and 16-bit SIMD integer operations. Its architecture is designed to enable high-quality audio in consumer electronics and embedded applications in a more cost-effective manner than is possible with DSPs.

Floating-Point Unit: All STM32 F4 devices also have an integrated floating-point unit (FPU). While signal-processing algorithms can be implemented using fixed-point arithmetic. this approach adds complexity in that underflow and overflow need to be manually managed. In addition, fixed-point processing offers less dynamic range than floating-point, which impacts many audio functions. With the integrated FPU, there is no penalty for retaining this precision. Code based on floating-point can also be substantially faster and requires less memory than fixedpoint code.

32-bit Efficiency: The bus size of the processor has a tremendous impact on both performance and power efficiency. Even if audio samples are streaming at 16 bits, the system still needs 32-bits to store intermediate computations. A 16-bit MCU or DSP, for example, requires seven operations (4 multiplies and 3 additions) just to complete a single 32 x 32 multiplication. The STM32 F4 can execute a 32-bit MAC (multiply and accumulate) with only one single-cycle operation.

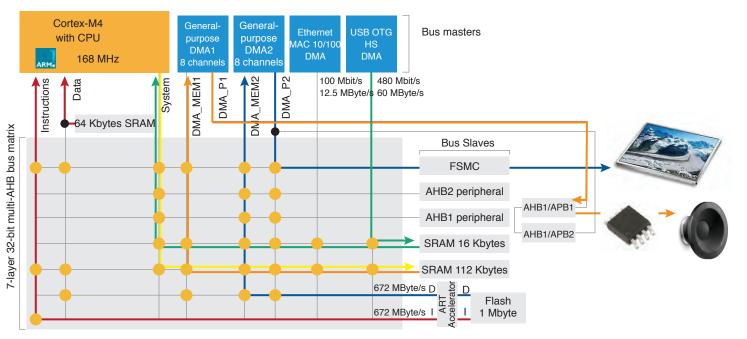

Figure 3 The multi-layer matrix that interconnects STM32 MCUs with peripherals and memory enables simultaneous transfer between multiple masters and slaves without requiring involvement from the CPU. This provides STM32 MCUs with a tremendous interconnect capacity that eliminates peripheral and memory access bottlenecks for the highest operating performance.

#### Multi-Layer Bus Fabric:

The key to real-time signal processing is maintaining efficient data flow. In a consumer audio device, however, the MCU must move not only signal data but manage program memory, communication ports, and other system tasks. The complexity and real-time nature of audio algorithms also requires them to be integrated with application code to ensure that neither core application tasks nor audio playback compromise each other.

The STM32 architecture is designed to minimize this problem so that developers do not need to spend time resolving potential conflicts. This is achieved through the low interrupt service overhead of STM32 devices combined with the multi-layer bus fabric that allows multiple DMA transactions to occur simultaneously without burdening the CPU. Figure 3 shows the high level of parallelism that can be achieved through simultaneous transfers over a multi-layer fabric:

- )) Program code is executed from Flash with data stored in SRAM (red)

- )) The compressed audio stream is received over USB and stored in SRAM (green).

- )) CPU with DSP and FPU functionality accesses the

compressed audio stream for decompression and signal processing (green)

- Decompressed MP3 data is sent from the CPU to SRAM (yellow)

- )) Audio data is output to I2S through DMA (orange)

- )) Graphical icons are transferred from Flash to the display through DMA (blue)

#### **Communications Interfaces:**

Users want to be able to access audio data from different sources and over different interfaces. With the right mix of interfaces including USB (host and device), Ethernet for Internet Radio, SDIO, and external memory developers can create flexible devices that support a wide range of usage models.

In addition to being able to receive data without loading the CPU, developers need to be able to address the many issues related to streaming audio, including lost packets and lack of feedback controls. For example, USB feedback controls to prevent under and overflow of the audio buffer are not always used or well implemented. This can result in lost or dropped packets that impact audio quality. To overcome this limitation, developers can utilize sample-rate conversion (SRC). SRC is also useful for converting between audio speeds (i.e., clock domains) while maintaining audio fidelity, compensating for slight mismatches in clock speed, or for mixing audio from different sources. For applications that need SRC, the STM32 F4 requires only 10% utilization, leaving plenty of headroom for other signal-processing tasks.

#### **Multiple Clock Sources:**

Consumer audio systems require a number of different clock domains—including the CPU, USB, and I2S—that have fixed frequencies and need to be accurate as well as free of jitter. Trying to use the same clock for each of these can impact precision. For example, it is straightforward to achieve a clean clock at 168 MHz for the CPU, 44.1 KHz for an I2S interface or 48 MHz for USB but not for all three using a single clock source.

The STM32 F4 integrates two PLLs for increased clocking flexibility. The main PLL is used to generate the system clock and the second PLL is available to generate the accurate clocks needed for high-quality audio.

|                      | STM32 F2<br>CPU load | STM32 F4<br>CPU load | Flash<br>footprint | RAM<br>footprint |  |

|----------------------|----------------------|----------------------|--------------------|------------------|--|

| MP3 decoder          | 17%                  | 6%                   | 23k                | 12344            |  |

| MP3 encoder          | 22.5%                | 9%                   | 25k                | 16060            |  |

| WMA decoder          | 17.5%                | 6%                   | 45k                | 36076            |  |

| AAC+ v2 decoder      | 25%                  | 11%                  | 54k                | 87000            |  |

| Channel mixer        | 2.5%                 | 2%                   | 0.6k               | 16               |  |

| Parametric Equalizer | 16%                  | 12%                  | 2k                 | 300              |  |

| Loudness Control     | 4.5%                 | 3.5%                 | 3.25k              | 632              |  |

| SRC                  | 22.5%                | 10%                  | 17.5k              | 1880             |  |

Complete audio system

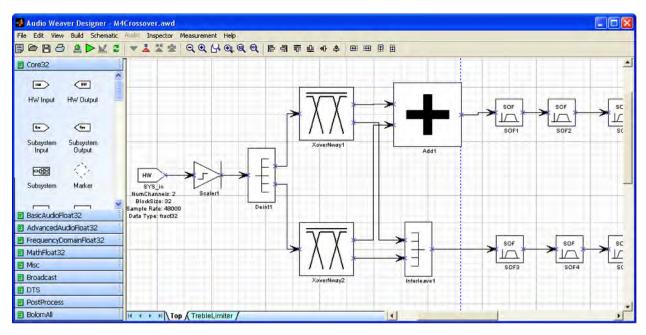

Figure 4 When computing 16- and 32-bit DSP functions, theSTM32 F4 offers a 25–70% improvement. As a result, systems can drop into sleep mode faster to conserve power or run more algorithms to further improve audio quality.

In addition to being able to receive data without loading the CPU, developers need to be able to address the many issues related to streaming audio, including lost packets and lack of feedback controls. For example, USB feedback controls to prevent under and overflow of the audio are not always used or well implemented.

The ability to source different clock domains enables designs based on the STM32 architecture to maintain a permanent USB connection and avoid audio synchronization issues.

#### **Integrated Audio Interfaces:**

The STM32 F4 has two fullduplex I2S standard stereo interfaces offering less than 0.5% sampling frequency error. There is also an external clock input to the I2S peripheral if an external high-quality audio PLL is preferred. In addition to simplifying design, integrating the I2S interfaces reduces component count, board size, and system cost.

**MCU Peripherals:** The STM32 architecture includes all of the real-time peripherals required for even the most demanding MCU-based application.

The combination of the STM32 F4's capabilities brings a new level of performance to audio applications. Performing a long 32-bit multiply or multiply-accumulate (MAC) operation on an STM32 F2, for example, takes 3-7 cycles. With the STM32 F4, this operation is performed in a single cycle. When computing 16- and 32bit DSP functions, the STM32 F4 offers a 25-70% (see Figure 4) improvement. As a result, systems can drop into sleep mode faster to conserve power or run more algorithms to further improve audio quality.

In addition to the integrated DSP capabilities of the STM32 F4, developers have access to the

CMSIS DSP library to accelerate development. The CMSIS DSP library includes a large number of DSP and floatingpoint functions optimized for the algorithms commonly used in audio applications. This library is supplied by ARM for processors built around the Cortex-M4 processor, DSP Concepts is the company that wrote the CMSIS DSP library. They have leveraged their intimate knowledge of the library to create the audio blocks that make up their signal processing design tool, Audio Weaver.

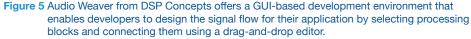

### Audio Algorithm Design

Audio Weaver enables developers to quickly design the audio processing portion of their system; i.e., everything that goes on between receiving an audio signal and outputting it. Audio Weaver offers a **GUI-based development** environment that enables developers to design the signal flow for their application by selecting processing blocks and connecting them using a drag-and-drop editor (see Figure 5). Each block has handoptimized code behind it, and the tool automatically creates the required data structures.

Because complex functions are built from base audio functions, the final code executes with no performance or efficiency losses compared to handcoding from scratch.

When algorithm code is written by hand, each design iteration requires substantial time investment since the code must be optimized and tuned to see what its actual impact on sound quality and processing load are. With Audio Weaver. the design cycle is much faster, giving developers the ability to explore more configurations in their efforts to increase sound quality while reducing system cost. Code is highly optimized for MIPS and memory usage, supports floating-point processors such as the STM32 F4, offers flexible deployment modules, and does not require an RTOS to operate. The library includes over 150 different audio blocks, including thirdparty IP.

With tools like Audio Weaver, it has become possible to create highly tuned audio applications without engineers needing to have a deep knowledge of audio processing. For companies new to audio, complete reference designs are available, with assistance from DSP Concepts to tune them for the final production system. Companies that are comfortable with audio processing can work with individual audio blocks that provide basic functionality and build them into higher-level processing value-add of Audio Weaver is faster time-to-market.

### Accelerating Optimization

To speed design, Audio Weaver supports cross-platform development. The ability to run the same algorithms on a PC as on the STM32 F4 gives engineers a powerful environment in MIPS and memory required by each audio processing stage. This enables engineers to measure how much a particular improvement in sound quality will cost in terms of CPU utilization to determine the most efficient use of processing resources when many functions have to operate simultaneously.

When algorithm code is written by hand, each design iteration requires substantial time investment since the code must be optimized and tuned to see what its actual impact on sound quality and processing load are. With Audio Weaver, the design cycle is much faster, giving developers the ability to explore more configurations in their efforts to increase sound quality while reducing system cost.

algorithms. Even sophisticated companies can accelerate design using Audio Weaver as it provides a framework with core components that not only jumpstarts design with highly optimized code but provides a development environment that facilitates fast prototyping and tuning. For these companies the

which to design and tune the software in parallel with hardware development. Once target hardware is available, the code can be retargeted for the STM32 F4 and final optimizations made, resulting in significant time-tomarket savings.

During final optimization, developers can profile the

Consider the use of different order filters to equalize the speakers. A lower-order filter, for example, may provide a frequency response that is 3 dB off of the ideal response while a higher order filter is off by only 1 dB. The relative difference in CPU utilization between these two filters can be used to determine where to allocate CPU resources to maximize sound quality.

At the end of the day, however, audio quality is not about response graphs but how it actually sounds to people. With many development systems, engineers have to make adjustments to code, recompile, and download code before they can hear a new configuration. However, to assess the impact of a lower-order filter on quality, for example, developers need to be able to hear both configurations right after each other.

Audio Weaver solves this problem by supporting a tuning interface that can change filter characteristics in real-time. With the ability to configure and switch between multiple settings with the click of a button, developers can compare two sets of speaker equalizations or different spatial processing. Note that the tuning interface is seamless and transparent, compared to instrumenting code that can impact quality because of extra loading on the CPU.

The ability to tune quickly and easily without recompiling can substantially shorten the time it takes to optimize a system. Flexible tuning also simplifies the optimization process for developers new to audio.

Note that audio applications are not comprised solely of audio processing. To accelerate system design, DSP Concepts also provides an extensive range of software functionality beyond its extensive audio module library, including:

)) Real-time kernel

- >> Audio I/O management

- >> PC/host control interface

- )) Boot loader

- )) Update manager

- )) Flash file system

### System-level Design

One of the challenges to adding audio to embedded designs is that while many MCU manufacturers offer reference designs, audio is typically not one of the applications supported.

To address this shortcoming, ST has invested significantly in creating digital audio resources for its customers in order to offer complete audio reference designs as well as tools that enable the design of quality audio optimized for the STM32 architecture. For example, ST and its partners offer a variety of evaluation boards with audio capabilities. ST also offers several docking station reference designs that provide a representative design that can be used in a wide range of embedded applications.

For Apple Made for iPod (MFI) licensees, ST offers the Apple iAP application, a complete solution based on STM32 F2 and STM32 F4 devices to deliver a high-quality music experience. The Apple iAP application support both simple accessory and audio streaming accessory for iPod, iPhone, and iPad devices. Components include:

- )) Either the STM322xG-EVAL or STM324xG-EVAL board to which developers connect their Apple Authentication Coprocessor (ACP) circuit

- )) Free Apple "iPod Accessory Protocol" (iAP) firmware with Lingoes for authentication and control/information data

- )) Free USB Host Library with USB Host HID class for control and information data

For audio streaming accessories, the Apple iAP application also supports:

- )) Free USB Host Library USB Host Audio classes

- )) Remote iPod/iPhone/iPAD control

- >> Digital audio streaming

- >> Music tag extraction

- )) Flash card reader capabilities, such as using an SD card or MMC, that can decode audio files from this media. Optimized decoders are provided for this purpose free of charge

Todav's consumer audio devices are complex systems that require both high performance to support quality playback and flexibility to meet rapidly changing market expectations. With its high performance core, efficient multi-layer bus fabric enabling simultaneous data transactions, and the right mix of MCU peripherals and connectivity, the STM32 F4 is an ideal architecture for many embedded and consumer audio applications. Developers can now design systems offering synchronized digital audio playback of the highest quality using a single MCU.

### Bringing Floating-Point Performance and Precision to Embedded Applications

By Olivier Ferrand, Application Engineer, STMicroelectronics Stephane Rainsard, Application Engineer, STMicroelectronics Abdelhamid Ghith, Application Engineer, STMicroelectronics

Hardware-based floating-point capabilities have long been an option on high-end MPUs and DSPs designed to serve as computational workhorses. Embedded systems based on MCUs, however, have classically used a fixed-point implementation.

There are many reasons for this. The types of simple calculations embedded systems needed to make could be handled sufficiently using fixed-point math. The resulting code was not only well-suited to an MCU's native mathematical capabilities, it resulted in faster execution and was more memory efficient than an equivalent floating-point implementation would be. The only disadvantage of using fixed-point was the tradeoff between range and precision, which could be tolerated in most cases.

Some of today's embedded systems are completely different from their early predecessors. They operate at high clock speeds and need to perform more complex calculations than ever before. While processing and memory efficiency are still primary design considerations, a more useful range and higher precision have become essential in many applications.

For example, to output high quality audio, MCUs need to support a wide dynamic range so that the system sounds good at both low and high frequencies. Medical applications, such as heart-rate monitors and glucose meters, need to measure more subtle signals and quantities. For industrial applications, higher precision in the MCU enables developers to use lower quality components in other parts of the system, reducing overall system cost. And with the increasing use of capacitivesensing technology, nearly every embedded application can benefit from detecting user inputs with greater accuracy, especially on displays with limited surface area.

### Floating-Point vs Fixed-Point

The balanced combination of range and precision in a floatingpoint number comes from its separation of the exponent and mantissa. When a number is stored in a fixed-point format, the position of the exponent is assumed and all of the bits are reserved for the mantissa (i.e., the actual digits used to represent the number). The issues that arise with fixed-point formats are similar to those associated with reading an ADC: the wider the range of values to be represented, the less resolution

there is at the lower end of the range. If very small changes in value need to be captured, the range must be more narrow. Developers, then, must choose between range and resolution.

Floating-point addresses these issues by dedicating a few bits to an exponent to track the decimal point. For example, the singleprecision format supported by the STM32 F4 uses one bit for the sign and 8 bits for the exponent, leaving 23+1 bits for the mantissa (the normalized format used adds an implicit bit to the 23 bits stored in the floating-point number). As such, a single-precision floating-point number gives a more useful range and precision combination compared to 8-, 16-, or even 32-bit fixed-point numbers which either give a wide range with greatly reduced precision or higher precision with a much smaller range.

The 32-bit single-precision format is part of the IEEE 754 Floating-Point Arithmetic standard. This standard represents decades of experience and provides a common approach for supporting floating-point arithmetic that unifies processors, coding tools, and high-level design tools. Specifically, the 754 standard is the basis for the floating-point data types used in C. In turn, these floating-point C formats are used in code generated by highlevel modeling/Meta language tools like MATLAB and Scilab.

One of the key benefits of using floating-point is that it enables developers to make more efficient use of C and powerful algorithm development tools that have previously been reserved for DSP- and MPU-based design. Generally speaking, floating-point numbers are easy to manipulate in C. High-level tools further accelerate and simplify development by enabling developers to describe complex algorithms in equation form and then quickly generate efficient C code rather than requiring them to hand-code algorithms in assembly. In addition, these high-level tools offer tremendous flexibility in allowing developers to rapidly implement changes

to algorithms without having to completely rewrite and reoptimize algorithm code. The end result is significant savings in development time and cost savings. Such tools also offer a powerful means for developers to test and validate applications.

### Software-based Floating-Point

In the past, developers had a limited number of ways in which they could utilize floatingpoint technology in MCUbased designs to increase computational precision. Introducing a second processor to handle calculations was often too expensive to consider. Alternatively, while the design could be migrated to a powerful MPU or DSP, neither type of architecture is as well-suited for the real-time demands of embedded systems as an MCU.

The availability of highperformance MCUs made it possible for developers to bring in a floating-point library to perform calculations in software. While such libraries enabled developers to use floating-point algorithms, they came at the expense of significantly reducing system throughput.

Such libraries also tended to be guite large and introduced significant processing overhead. For example, every operation between two numbers had to first align the numbers to have the same exponent and then, after performing the operation, round the result and code it back into the fixed-point format. While all of these actions were performed by the floating-point library and were not directly visible to developers, they still resulted in significantly degraded performance, greater processing latency, and an increased memory footprint.

the C code generated by the tool into a fixed-point implementation. The downside of this approach is the significant time investment required to adapt the code combined with the inflexibility to easily modify the algorithm later in the design cycle.

### The STM32 F4 Advantage: Integrated Floating-Point Technology

To stay competitive, developers of precision and high-performance embedded systems need to have access to floating-point functionality without sacrificing performance or memory efficiency

To stay competitive, developers of precision and high-performance embedded systems need to have access to floatingpoint functionality without sacrificing performance or memory efficiency.

If none of these alternatives was feasible and developers still needed the flexibility that highlevel modeling tools bring to the design process, they had the alternative to manually convert the floating-point operations in through the use of a softwarebased floating-point library or having to adapt the code by hand to a fixed-point implementation.

With the STM32 F4 MCU architecture, developers have

# World's highest STM32<sup>®</sup> F4 performance Cortex<sup>™</sup>-M MCU 168 MHz/210 DMIPS

STM32 Releasing your creativity

For further information, visit www.st.com/stm32f4

the option of bringing floatingpoint efficiency to an extensive range of low-cost embedded applications. The STM32 F4 integrates a floating-point unit (FPU) to execute these operations natively in hardware. The FPU is fully compliant with the IEEE.754 standard and has its own 32bit single-precision registers to handle operands and results. These registers can be viewed as double-word registers to enable more efficient load and store operations. The context of the FPU can be saved to the CPU stack using several methods based on the application architecture and whether registers need to be preserved or not.

The FPU supports the five different classes of numbers defined by the 754 standard - normalized. denormalized, zeros, infinites, and NaNs (Not-a-Number). It also supports the five exceptions of the standard-overflow. underflow. inexact, divide by zero and invalid operation-allowing applications to handle operations such as trying to compute the square root of a negative number (i.e., resulting in NaN + invalid operation exception). Exceptions are "untrapped", meaning that the FPU will return the result as specified by the 754 standard and raise an exception

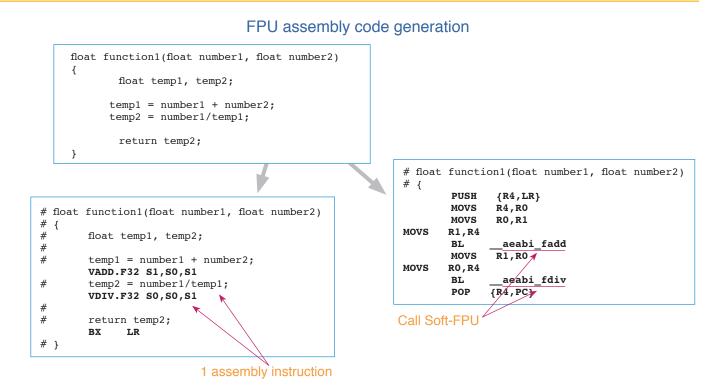

Figure 1 There is a significant reduction in code size when an integrated FPU is available (code on left) than when one is not (code on right).

flag. If needed, developers can also use the STM32 F4 floating-point global interrupt to address the issue.

The integrated FPU of the STM32 F4 offers a number of advantages to embedded designers:

- )) Access to the more useful range and precision that floating-point brings

- N Reduced coding complexity by being able to work with numbers in a more natural format

- )) Greater throughput compared to software floating-point libraries.

- Accelerated application development as C code generated by high-level tools can be used without modification or wrappers

- Smaller code footprint since instructions that used to be multiple lines of code in software libraries are now implemented with a single instruction

Simplified debugging as macro calls in floating-point libraries are eliminated

Effectively, the STM32 F4's FPU reverses the value proposition between fixed- and floating-point for many MCU-based designs.

### **Seamless Integration**

Figure 1 shows the difference between the assembly code generated when an FPU is available on an MCU as

```

void GenerateJulia fpu(uint16 t size x, uint16 t

size y, uint16 t offset x, uint16 t offset y, uint16 t

zoom, uint8 t * buffer)

{

float tmp1, tmp2;

float num real, num imq;

float radius;

uint8 t i;

uint16 t x,y;

for (y=0; y<size y; y++)</pre>

{

for (x=0; x < size x; x++)

{

num real = y - offset y;

num real = num real / zoom;

num img = x - offset x;

num img = num img / zoom;

i=0;

radius = 0;

while ((i<ITERATION-1) && (radius < 4))</pre>

tmp1 = num real * num real;

tmp2 = num img * num img;

num img = 2*num real*num img + IMG CONSTANT;

num real = tmp1 - tmp2 + REAL CONSTANT;

radius = tmp1 + tmp2;

i++;

}

/* Store the value in the buffer */

buffer[x+y*size x] = i;

}

}

}

```

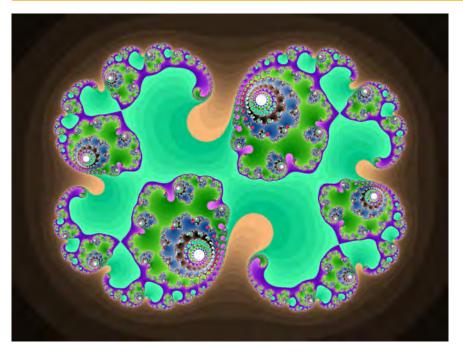

Figure 2 Algorithmic code, such as for the Julia set as shown here, requires no modification to take advantage of the STM32 F4's hardware-based floating-point capabilities.

compared to when one is not. The example is a simple one, adding number1 and number2 together and storing the result in temp1. Number1 is then divided by temp1 and stored in temp2.

When an FPU is available, the compiler directly uses native FPU instructions (see add and divide instructions in the code on the left). When an FPU is not available, however, the compiler inserts macro calls to the software floating-point library to perform the function (see code on the right). These functions comprise multiple instructions that take many more cycles to complete the calculation. Although the difference is only a few instructions, the extra overhead represents a high percentage of the algorithm's overall load on the CPU. When considered over the whole of an application, the impact on processing efficiency is tremendous.

### Performance by the Numbers

The following example clearly illustrates the benefit of having an integrated FPU. Figure 2 shows the code for a simple mathematical fractal known as the Julia set, given by the equation:

$$Z_{n+1} = Z_n^2 + C$$

where the sequence for each x+ i.y point is computed with:

$$c = c_x + i.c_y$$

This algorithm provides an effective way to show the impact on performance of the STM32 F4's FPU since no code modification is required to utilize it. In fact, the only difference is whether the FPU is activated during compilation.

Figure 3 shows the time spent for the calculation of the Julia set using different zooming factors. As can be seen, the presence of an FPU yields an increase in performance on the order of 11.5 to 17 times faster. Again, no modification to code is required, just selecting the FPU in the compiler options.

For applications that need to implement signal processing capabilities or operate on multiple data in parallel, STM32 F4 MCUs have a versatile architecture that also implements hardwarebased DSP capabilities. The availability of both an FPU and DSP instructions in the STM32 F4 provides developers with a full range of capabilities to

| Frame | Zoom | Duration<br>with FPU | Duration<br>without<br>FPU (microlib) | Ratio | Duration<br>without<br>FPU (no<br>microlib) | Ratio |

|-------|------|----------------------|---------------------------------------|-------|---------------------------------------------|-------|

| 0     | 120  | 222                  | 3783                                  | 17.04 | 2597                                        | 11.70 |

| 1     | 110  | 194                  | 3276                                  | 16.89 | 2243                                        | 11.56 |

| 2     | 100  | 167                  | 2794                                  | 16.73 | 1906                                        | 11.41 |

| 3     | 150  | 298                  | 5156                                  | 17.30 | 3558                                        | 11.94 |

| 4     | 200  | 312                  | 5412                                  | 17.35 | 3740                                        | 11.99 |

| 5     | 275  | 296                  | 5124                                  | 17.31 | 3540                                        | 11.96 |

| 6     | 350  | 284                  | 4905                                  | 17.27 | 3389                                        | 11.93 |

| 7     | 450  | 289                  | 4989                                  | 17.26 | 3448                                        | 11.93 |

| 8     | 600  | 273                  | 4705                                  | 17.23 | 3251                                        | 11.91 |

| 9     | 800  | 267                  | 4592                                  | 17.20 | 3173                                        | 11.88 |

| 10    | 1000 | 261                  | 4485                                  | 17.18 | 3100                                        | 11.88 |

| 11    | 1200 | 255                  | 4374                                  | 17.15 | 3023                                        | 11.85 |

| 12    | 1500 | 242                  | 4138                                  | 17.10 | 2860                                        | 11.82 |

| 13    | 2000 | 210                  | 3555                                  | 16.93 | 2455                                        | 11.69 |

| 14    | 1500 | 242                  | 4138                                  | 17.10 | 2860                                        | 11.82 |

| 15    | 1200 | 255                  | 4374                                  | 17.15 | 3023                                        | 11.85 |

| 16    | 1000 | 261                  | 4485                                  | 17.18 | 3100                                        | 11.88 |

| 17    | 800  | 267                  | 4592                                  | 17.20 | 3173                                        | 11.88 |

| 18    | 600  | 273                  | 4705                                  | 17.23 | 3251                                        | 11.91 |

| 19    | 450  | 289                  | 4989                                  | 17.26 | 3448                                        | 11.93 |

| 20    | 350  | 284                  | 4905                                  | 17.27 | 3389                                        | 11.93 |

| 21    | 275  | 296                  | 5123                                  | 17.31 | 3540                                        | 11.96 |

| 22    | 200  | 312                  | 5412                                  | 17.35 | 3740                                        | 11.99 |

| 23    | 150  | 298                  | 5156                                  | 17.30 | 3558                                        | 11.94 |

| 24    | 100  | 167                  | 2794                                  | 16.73 | 1906                                        | 11.41 |

| 25    | 110  | 194                  | 3276                                  | 16.89 | 2243                                        | 11.56 |

**Figure 3** This table shows the time spent for the calculation of the Julia set using different zooming factors. The presence of an FPU yields an increase in performance on the order of 11.5 to 17 faster with no modification to code required.

100 80 **10X improvement** Best compromise 60 Development time vs. 17.9X improvement performance Best performance 40 requires effort for proper data management 20 0 32-bit float 16-bit fixed-point 32-bit float no FPU FPU SIMD optimized

**FIR filter** execution time (using CMSIS DSP library)

**Figure 4** The relative time it takes to execute a FIR filter is 10X better when utilizing the STM32 F4's FPU. If more headroom is needed, the use of the 16-bit fixed-point SIMD (single instruction, multiple data) optimized instructions that are part of the DSP capabilities of the STM32 F4 increase performance by 17.9X.

implement the wide variety of algorithms embedded applications require. Each accelerates different types of processing and together they complement each other to enable the most optimized implementation based on performance, memory, and ease of programming.

The ease of migrating an existing application to seamlessly take advantage of the STM32 F4's integrated FPU capabilities is important as well. Consider an STM32 F2 application executing a floatingpoint FIR filter based on the CMSIS DSP library available through ARM. Figure 4 shows the relative time it takes to perform the FIR filter 100 times on an STM32 F2 with no FPU or DSP capabilities using a purely software implementation to make the necessary floatingpoint calculations.

When the same code is compiled for the STM32 F4 to leverage the FPU in hardware, there is

Figure 5 A top-level view of the Julia set.

an immediate 10X improvement in relative performance (i.e., factoring out the impact of clock speed). Just by changing processors and activating the FPU, there is a significant performance advantage. This one change to the design is enough to yield a tremendous amount of headroom for additional tasks, depending upon 17.9X, again not considering the application.

If more headroom is needed, the performance of the FIR filter can be further improved through the use of the 16bit fixed-point SIMD (single instruction, multiple data) optimized instructions that are part of the DSP capabilities of the STM32 F4. For example, when using the SIMD optimized FIR algorithm of the CMSIS library from ARM, the performance improvement is clock speed.

### **Unparalleled Flexibility**

Traditionally, when designing a DSP-based system, developers have to choose between fixedand floating-point architectures. Floating-point comes at a price premium, and manufacturers have had to balance this added cost against the extra complexity in application development that comes when using fixed-point. While the FPU is an optional component of the ARM Cortex-M4 architecture, ST has designed its STM32 F4 family so that every device offers an FPU. In this way, developers always have access to floating-point performance and precision without compromise.

The bottom line is that the STM32 F4 provides developers with a flexible, high-performance architecture that offers the realtime responsiveness of an MCU with the precise floating-point and digital signal processing capabilities that today's embedded designs need. The ability of the STM32 F4's FPU to perform fast mathematical computations on C-based float data is a key benefit for many application tasks that require precision, including loop control.

audio processing, sensor signal conditioning, digital media decoding, and digital filtering, to name just a few.

The availability of an FPU speeds complex algorithm development, all the way from high-level design tools down to software generation. Hardware native support for floating-point operations simplifies coding and substantially accelerates product development by enabling the most efficient implementation for any mathematical calculation. Code that has been generated by such tools to be used directly by the FPU will offer the highest level of performance.

The faster processing an FPU brings to applications offers either more headroom to support new functionality or faster time-to-sleep for powersensitive applications. It also enables developers to introduce more complex processing and functionality to applications than was previously possible with traditional MCUs. As a result, when implementing a mathematical algorithm on an STM32 F4, developers never have to choose between performance and development time.

### Achieving Ultra-Low-Power Efficiency for Portable Medical Devices

By Jean J. Labrosse, Founder, CEO and President, Micriµm Jim Lombard, Application Engineer, STMicroelectronics

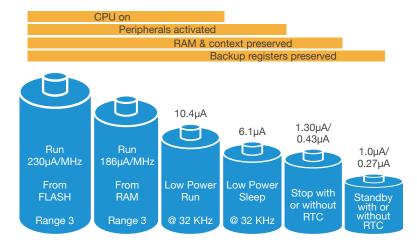

The availability of low-cost, fullfeatured microcontrollers has created a revolution in the health industry leading to equipment migrating from the hospital and into patients' homes. Designing these portable medical devices presents new challenges for engineers, such as implementing precision analog processing requiring complex calculations and creating a system that is simple and comfortable to operate even for physically-challenged users. In addition, these devices have to be able to run as long as possible without having to change or recharge batteries, even after sitting on a warehouse shelf for up to 18 months. To meet the unique requirements of portable medical devices, developers need an advanced processor architecture that combines performance, ultra-low-power process technology, low-cost, and efficient power management and communications capabilities.

### Designing for Medical Applications

Next-generation medical equipment is evolving along two primary paths: sports and personal health. Both markets require innovation that enables portable devices to collect more run-time data and complete advanced calculations to create a comprehensive profile of a person's current condition. Within personal health, developers also need to understand the special requirements of emerging disposable devices.

The portable medical device market is extremely strong. Consider that with 8.3% of the US population suffering from diabetes, a portable glucose meter is an essential tool for individuals who need to monitor their glucose for conceivably the rest of their lives. Similarly, an electrocardiogram (ECG) monitor enables people at risk for any number of conditions to record their ECG waveform at home. In addition to eliminating the need for multiple office visits, homebased testing gives doctors a more comprehensive patient history to work with.

Portable handheld medical devices have a stringent set of requirements (see Figure 1.) Given that prospective users can be from all walks of life, devices must be as simple to use as possible, with limited or no setup required. They also need to be comfortable to use and operable even by physically-challenged users. In general, the display must be large for ease of reading and utilize a minimum number of buttons to avoid confusing users. Ideally, as many functions as possible need to be automated so that users don't have to be trained how to use the device. If the device has a touchscreen, the GUI must be intuitive and have a limited number of

- )) Large display

- Minimal number of large operator buttons

- Batteries are easy to change, easy to recharge, or are sufficient to last for the operating life of the device

- Safe and accurate operation

- )) Low cost

- )) Low power

- Audio feedback

#### Figure 1 Common Product Requirements for Portable Medical Devices

operating modes. Both low cost and low power consumption are critical as well, and devices need to be able to run as long as possible without having to change or recharge the battery.

### Take your STM32-Based Products to the Next Level

Micrium's industry leading books take you far beyond product training. They give you in-depth knowledge of the inner working of Micrium's high-quality software components, with a focus on STMicroelectronics devices.

- μC/OS-III: The Real-Time Kernel

- µC/TCP-IP: The Embedded Protocol Stack

Micriµm products are created for engineers by engineers.

Contact us to discuss your project requirements, challenges, and goals.

www.Micrium.com

An important trend in medical applications is the use of disposable devices. Highvolume devices such as heartrate monitors can provide medical professionals with important data that is useful in identifying issues before they become full-blown problems; e.g., by having a patient track his or her heart rate for a few weeks after an operation, a doctor can verify the patient's successful recovery.

The use of disposable devices offers many benefits. Rather than require patients to purchase a monitoring device designed to operate for years, the hospital can provide a "disposable" version that can perform the task reliably for weeks at a significantly lower cost. This strategy also enables hospitals to leverage innovations in technology faster.

Designing a medical device for limited use, however, substantially shifts the design mindset. For example, device cost becomes significantly more important when the revenue stream from consumables is weeks rather than years. Devices also have to be ready to operate out-of-the-box, so parameters such as which test strips are going to be used need to be preprogrammed into devices by manufacturers. Power efficiency becomes more critical as well. Even though they will only be used for a handful of weeks, devices may first sit on the shelf for up to 18 months. During this time, the device is in a low power mode with the real-time clock running. With an ultra-low-power MCU, it is possible to achieve this without requiring the user to change batteries.

### The STM32 Architecture